FAIRLIGHT COMPUTER MUSICAL INSTRUMENT

# All about Fairlight

PDF format by *Jean-Bernard Emond & David Cilia* Jean-Bernard.Emond@paris4.sorbonne.fr http://jupiter.paris4.sorbonne.fr

Version 1.0 18 février 2001

Warning this Service Manual is only for

Fairlight Computer Musical Instrument Model IIx

For more information about other FAIRLIGHT products and company today www.fairlightesp.com.au

This manual is © Fairlight ESP Pty. Ltd.

CMI SYSTEM SERVICE MANUAL

FAIRLIGHT INSTRUMENTS, FEBRUARY 1985

Revision 2.1

# TABLE OF CONTENTS

| 1,         | INTRODUCTION TO C.M.I. MAINFRAME  1.1 SYSTEM OVERVIEW  Figure 1. C.M.I. SYSTEM BLOCK OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                   | Page<br>1<br>1<br>2                                                                |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 2.         | FUNCTIONAL DESCRIPTION 2.1 COMPUTER SECTION (MAINFRAME) 2.2 GRAPHICS TERMINAL 2.3 MUSIC KEYBOARD 2.4 ALPHA-NUMERIC KEYBOARD 2.5 INTERCONNECTING CABLES                                                                                                                                                                                                                                                                                                                          | <b>-</b>                                                                           |

| 3.         | TROUBLESHOOTING 3.1 SUB-SYSTEM SUBSTITUTION 3.2 SUB-SYSTEM NON-SUBSTITUTION                                                                                                                                                                                                                                                                                                                                                                                                     | 5<br>5<br>6                                                                        |

|            | Figure 2. C.M.I. SYSTEM INTERCONNECTION CABLES 4.1 Mains Cable: MC068 (I.E.C.) 4.2 Graphics Terminal Power: MC067 (I.E.C.) 4.3 Graphics Terminal Signal: MC065 4.4 Music Keyboard Power: MC064 4.5 Music Keyboard Signal: MC060 4.6 Alpha-numeric Keyboard Power/Signal: MC013 4.7 Slave Keyboard Power/Signal: MC059 4.8 Printer: MC062 4.9 Phones 4.10 Monitor 4.11 Channels 1 to 8 4.12 Mixed Line Out 4.13 Sync 4.14 Filter Output 4.15 Mic In 4.16 Line In 4.17 ADC Direct | 8<br>9<br>9<br>9<br>10<br>11<br>12<br>12<br>13<br>13<br>14<br>14<br>14<br>15<br>15 |

| ō <b>.</b> | REPAIR PROCEDURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                 |

| · .        | PREVENTATIVE MAINTENANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    |

#### 1. INTRODUCTION

The Fairlight Computer Musical Instrument is a complete music production and performance instrument. It is a special purpose computer system incorporating a custom dual M6809 central processor interfaced to special input-output devices optimised for the rather unusual requirements of music production.

The information presented in this manual is intended as a guide to give the reader an appreciation of the general operating principles of the C.M.I. In the event of a malfunction, it should be used to isolate which of the four main C.M.I. sub-systems is at fault, then for detailed functional information refer to the service manual for the item concerned.

Related documents are:

C.M.I. MAINFRAME SERVICE MANUAL GRAPHICS TERMINAL SERVICE MANUAL ALPHA-NUMERIC KEYBOARD SERVICE MANUAL MUSIC KEYBOARD SERVICE MANUAL FLOPPY-DISK DRIVE SERVICE MANUAL

#### 1.1 SYSTEM OVERVIEW

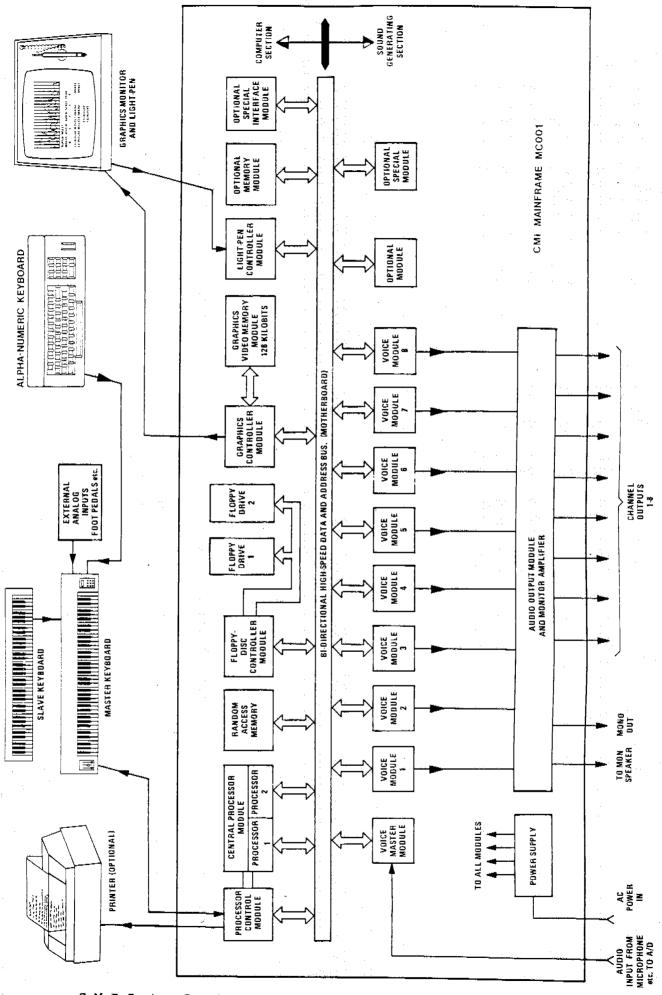

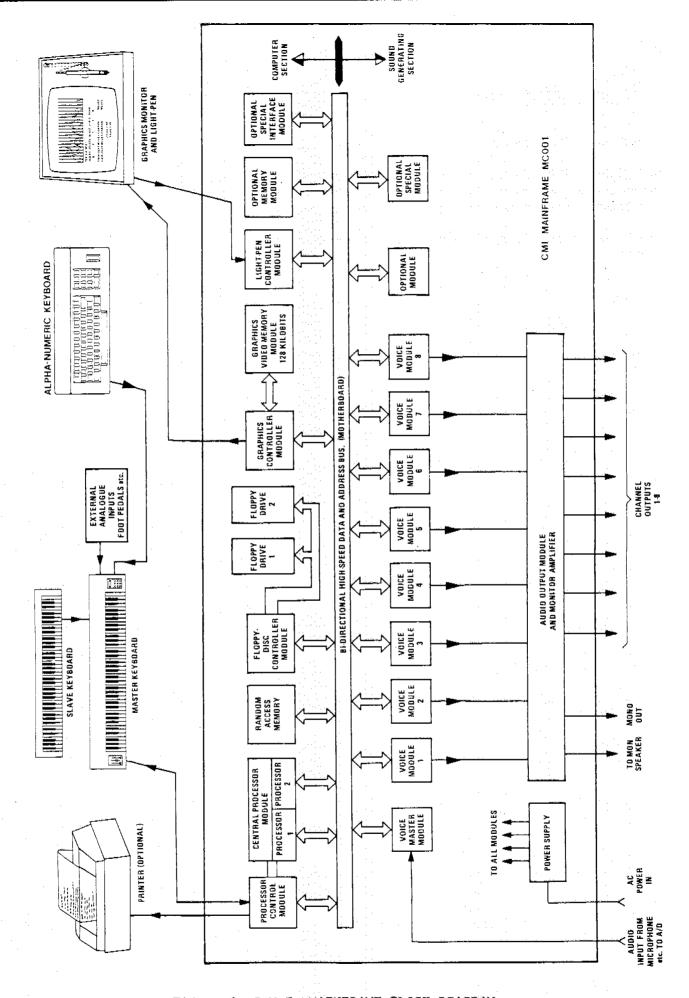

The system comprises for main units (Refer Fig. 1).

- 1) Mainframe: Houses the computer section, floppy disk drives, audio generation section and power supplies.

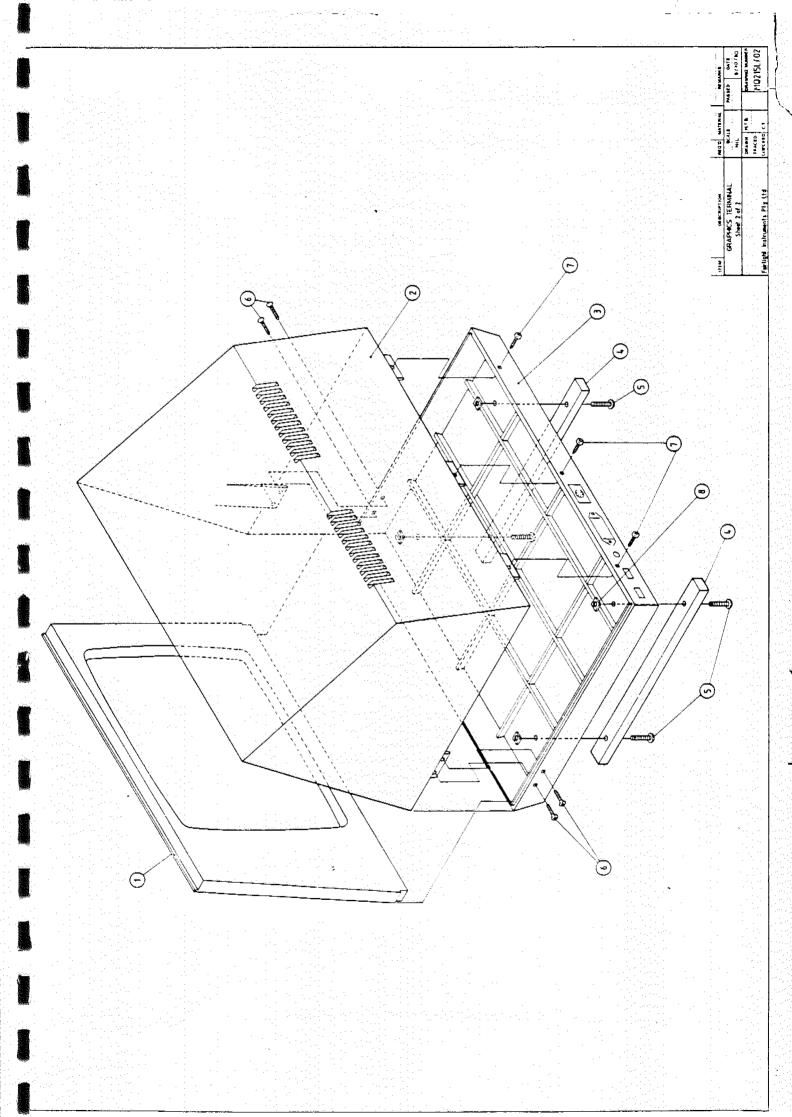

- 2) Graphics Terminal: The primary display terminal for the computer. It is a 15 inch C.R.T. display with lightpen.

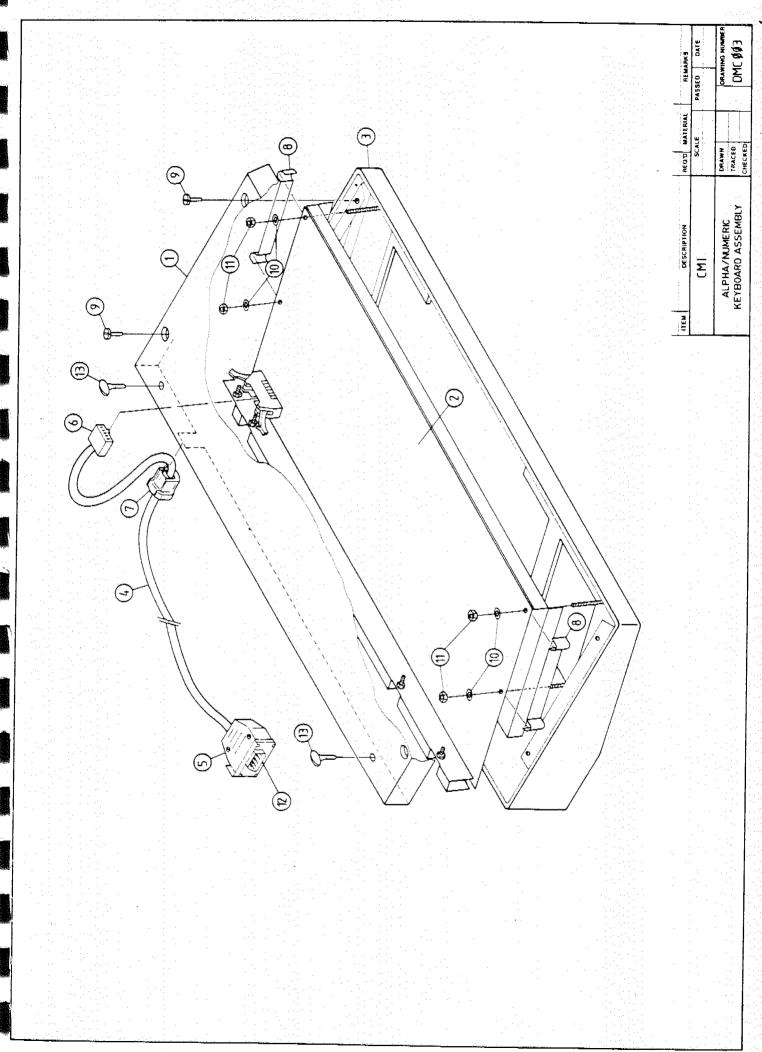

- 3) Alphanumeric Keyboard: Sends serial ASCII data to the computer. Used for operator input of commands etc.

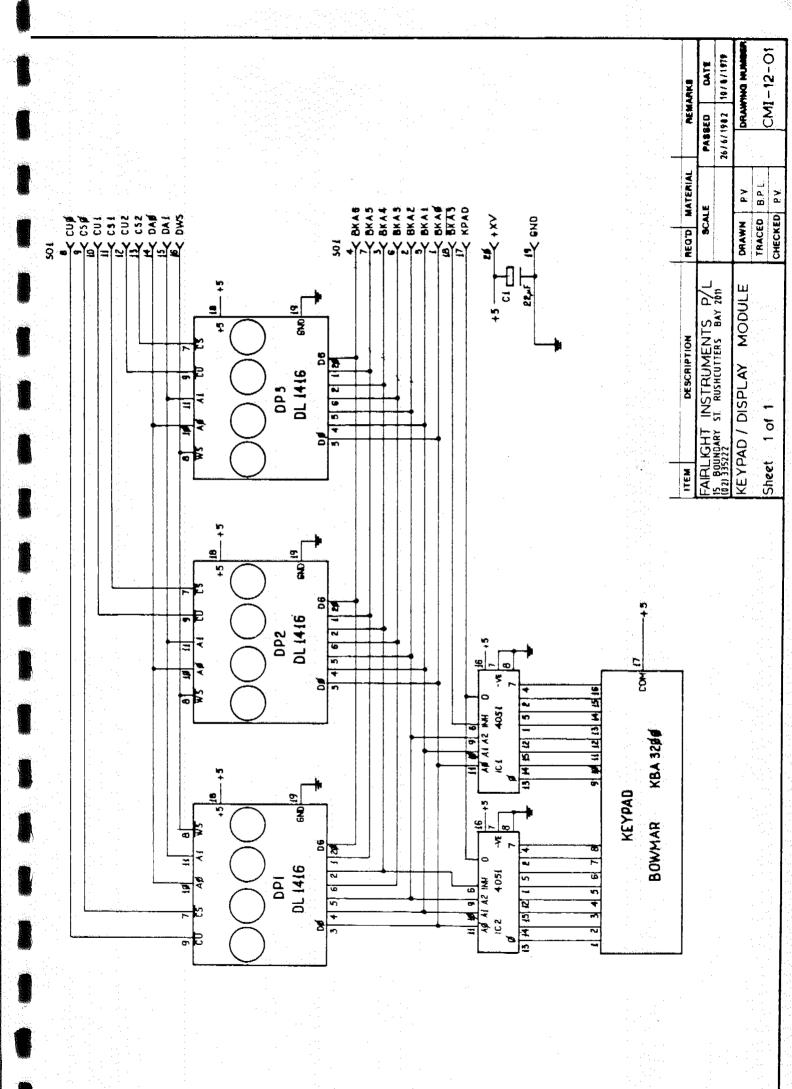

- 4) Music Keyboard: Piano-like keyboard sends serial data to the computer on each key depression. Used for live playing. Also includes several analog controls and switches which are digitised, and a numeric keypad with 12 character alpha-numeric display which serves as a secondary Input-Output device.

C M I System Service Manual

Page 2

### 2. FUNCTIONAL DESCRIPTION

## 2.1 COMPUTER SECTION (MAINFRAME)

The computer section of the C.M.I. houses all the digital control and sound generating hardware. It can be considered a stand-alone operational unit. With nothing connected to it it is possible to start up the system and bootstrap load the disks (BOOT the system). On power-up, EPROMS located on the C.P.U. Control Card Q-133 will control the Boot process.

As soon as a disk is placed in the left-hand drive (Drive 0) a special sector known as the Boot Block is read into RAM and executed. The code in the Boot Block then completes the Boot by reading in the C.M.I. Operating System. The system is then ready to accept commands from the alpha-keyboard, music keyboard or light pen.

For deatailed information refer to the C.M.I. MAINFRAME SERVICE MANUAL.

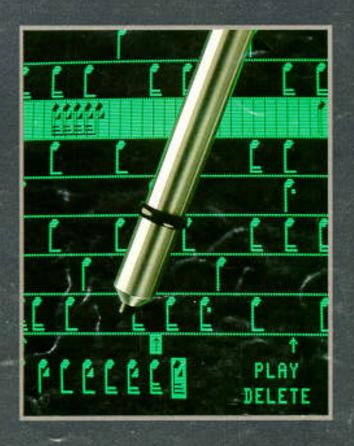

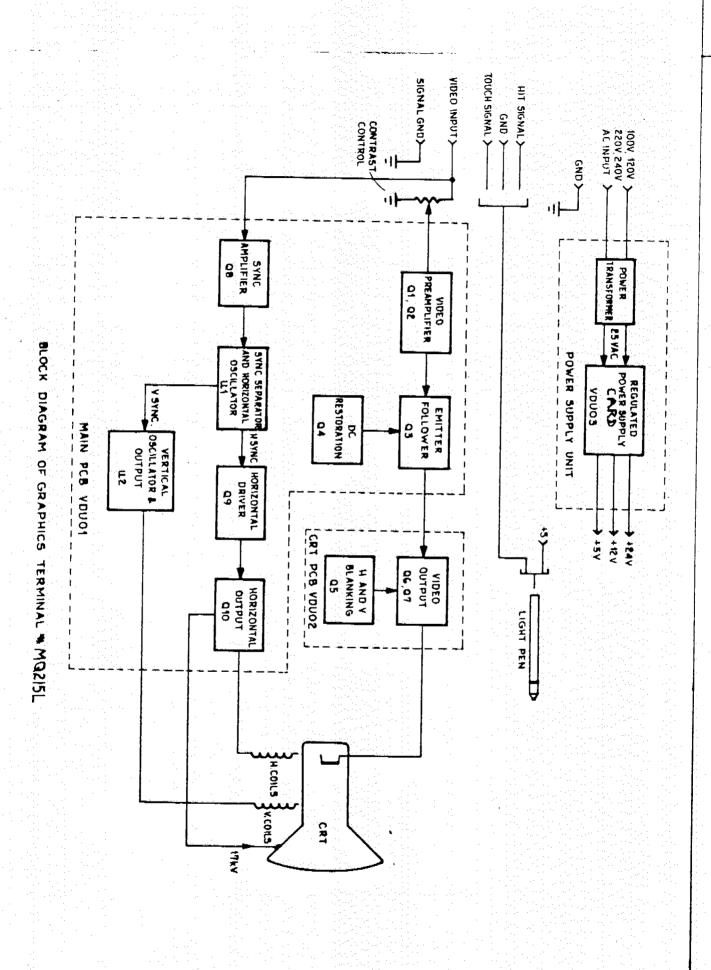

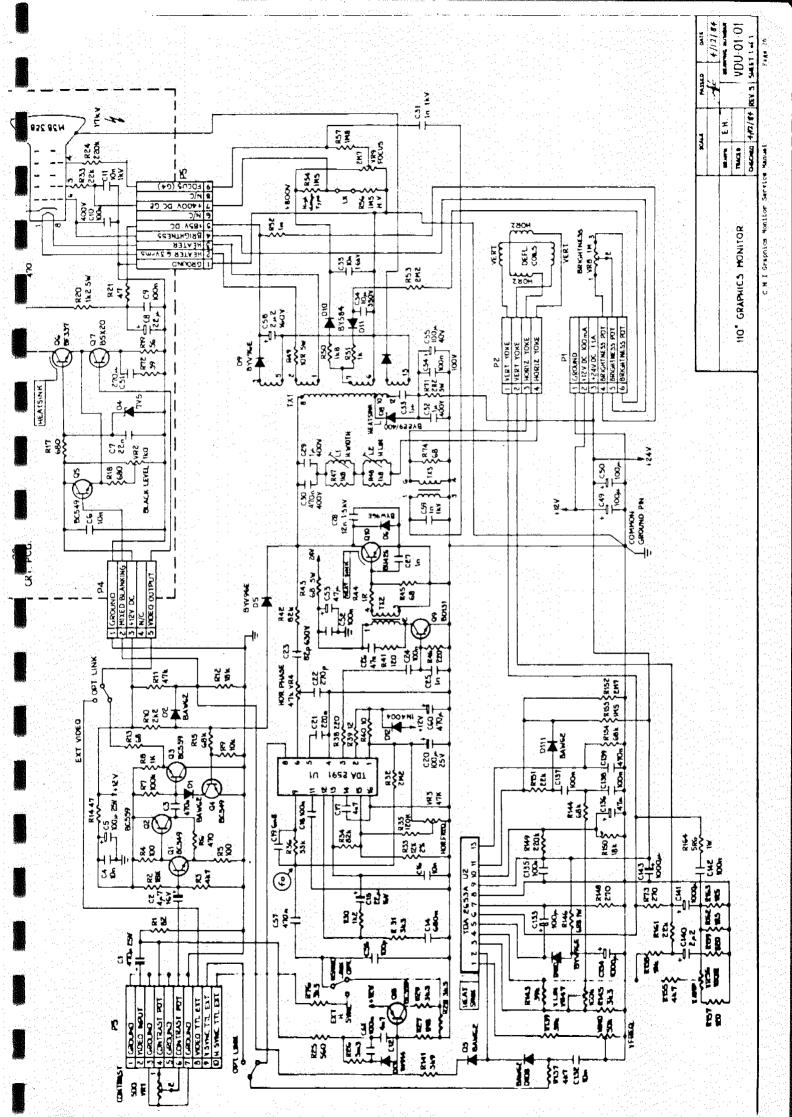

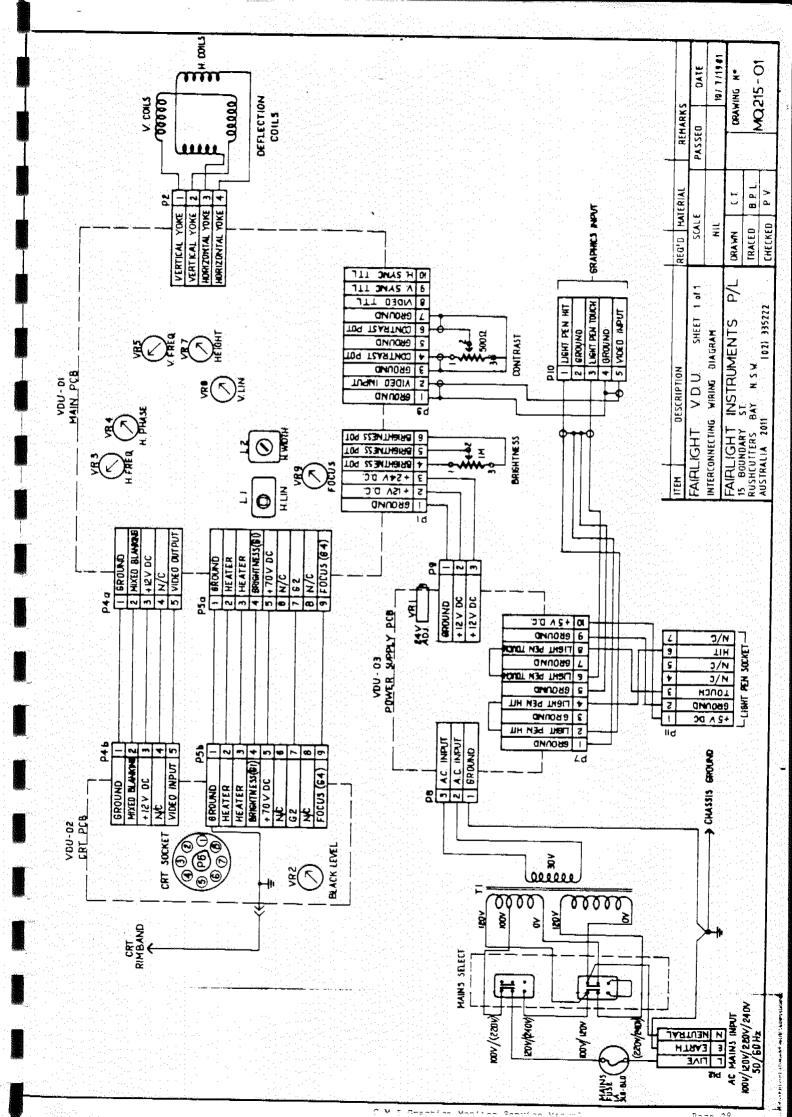

#### 2.2 GRAPHICS TERMINAL

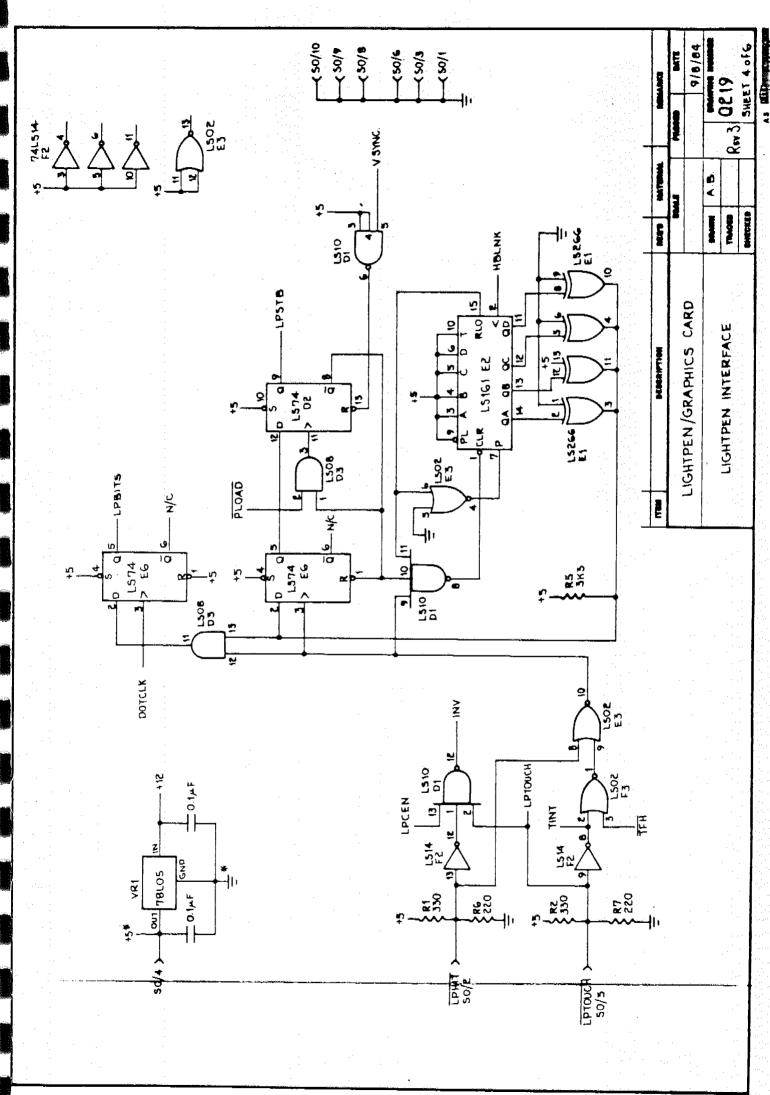

Display data for the Graphics Terminal is generated by the Graphics Display card Q-219 in the form of a composite video signal. The display format is a bit-mapped image of 16 kilobytes of VRAM, displayed as a 512 (Horizontal) by 256 (Vertical) matrix.

The Light-Pen operates by sending a pulse back to the computer when the phosphor dot is "seen" to flash past. The Light Pen Interface Q-219, located in the Mainframe generates X-Y co-ordinates from the timing of this pulse. As well as this "Hit" signal from the lightpen, there is a "Touch" signal, which indicates that the operator has activated the pen by touching the tip.

For detailed information, refer to the GRAPHICS TERMINAL SERVICE MANUAL.

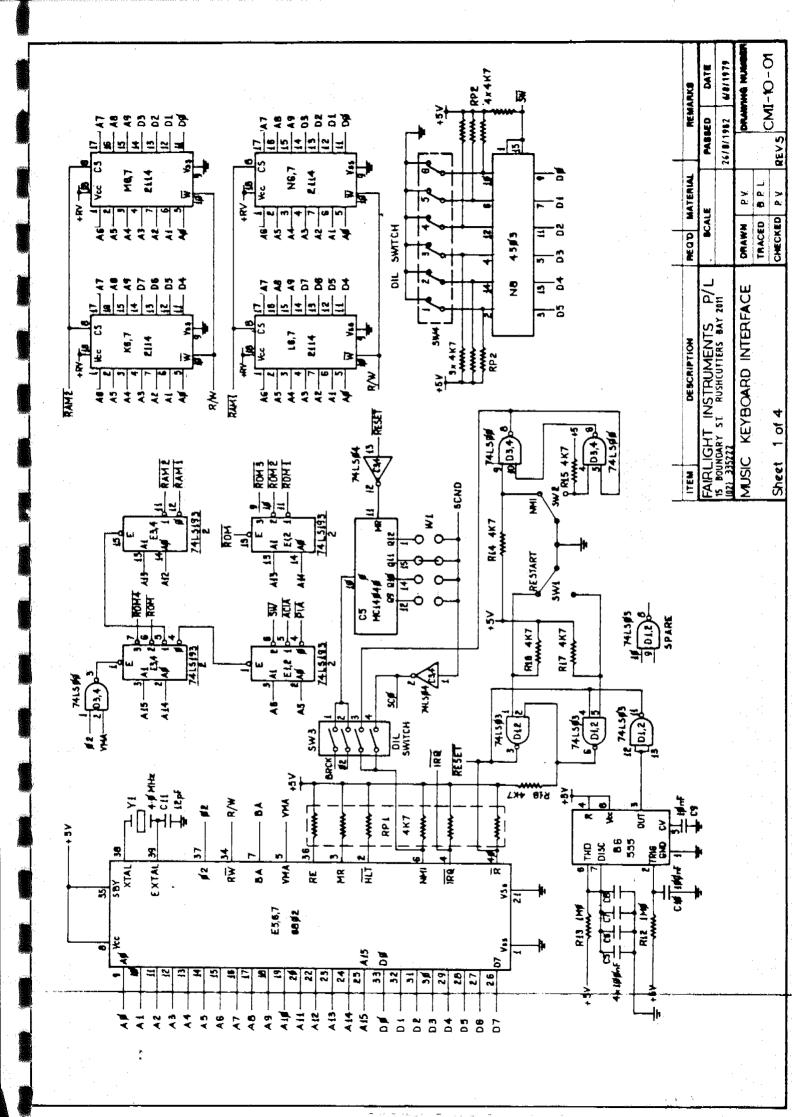

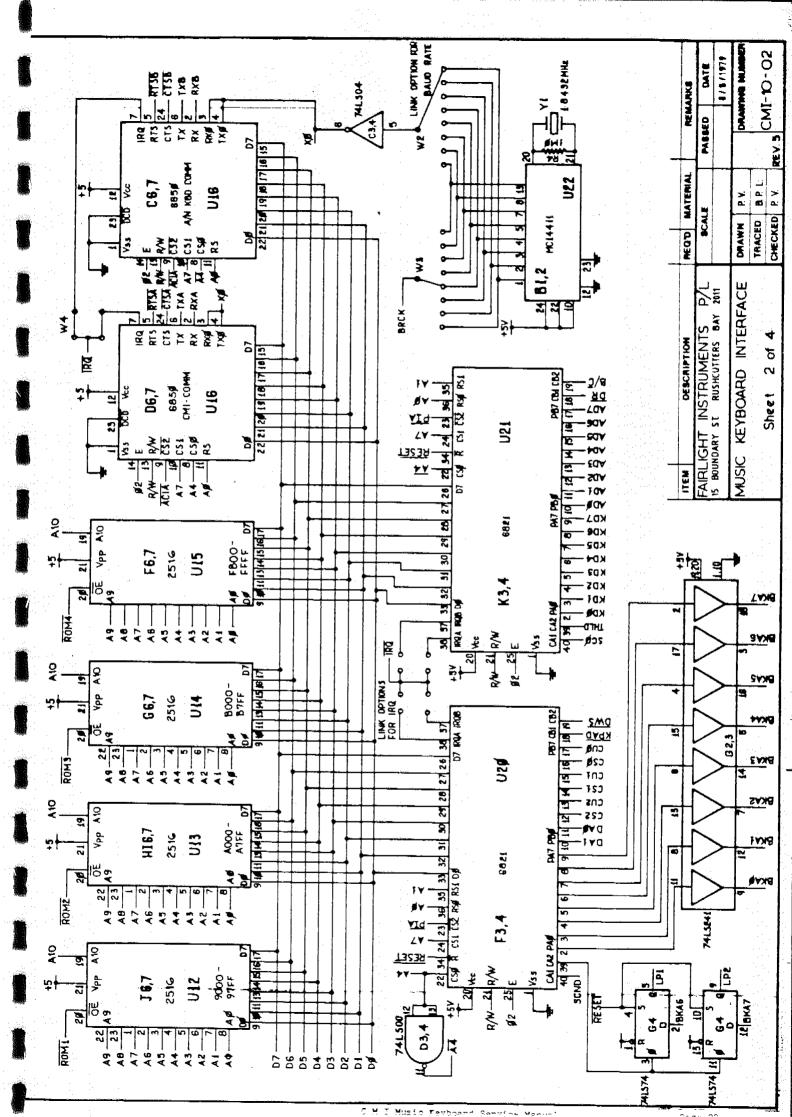

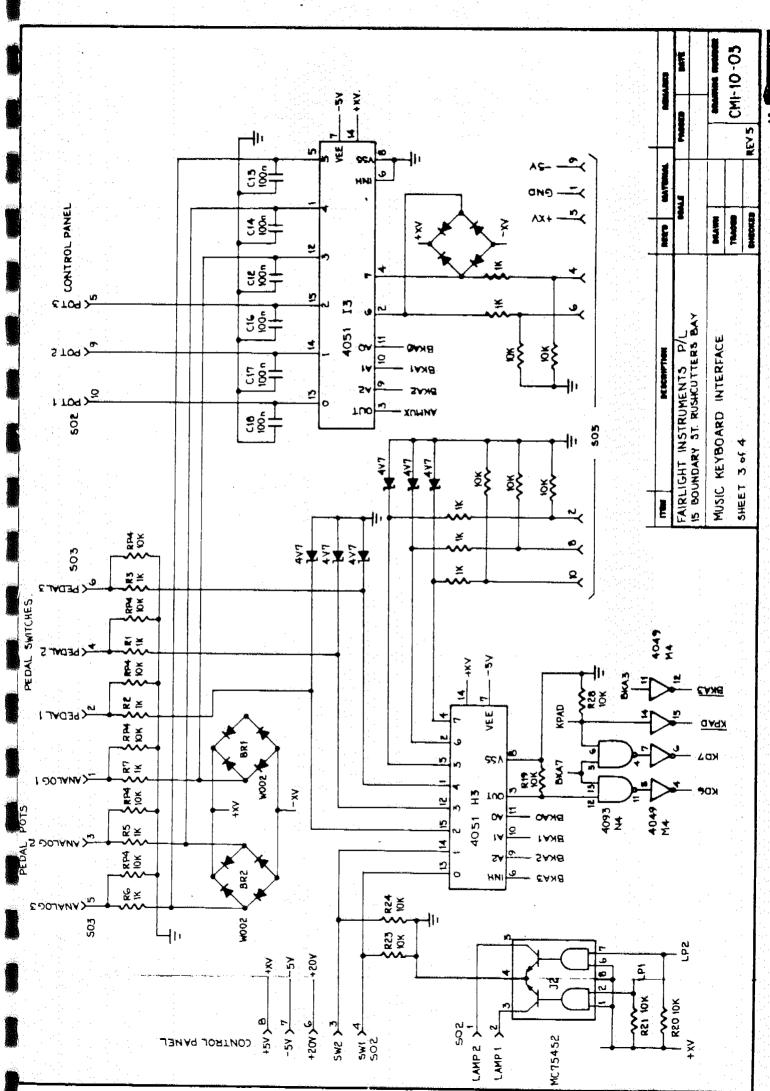

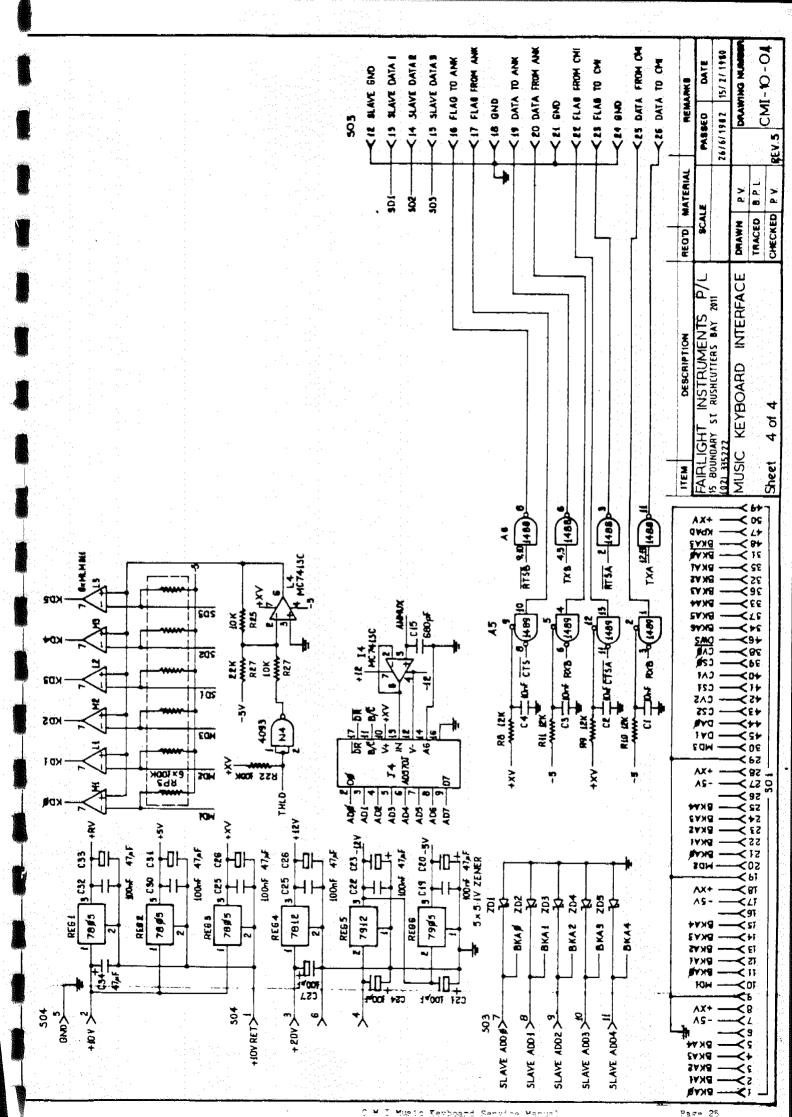

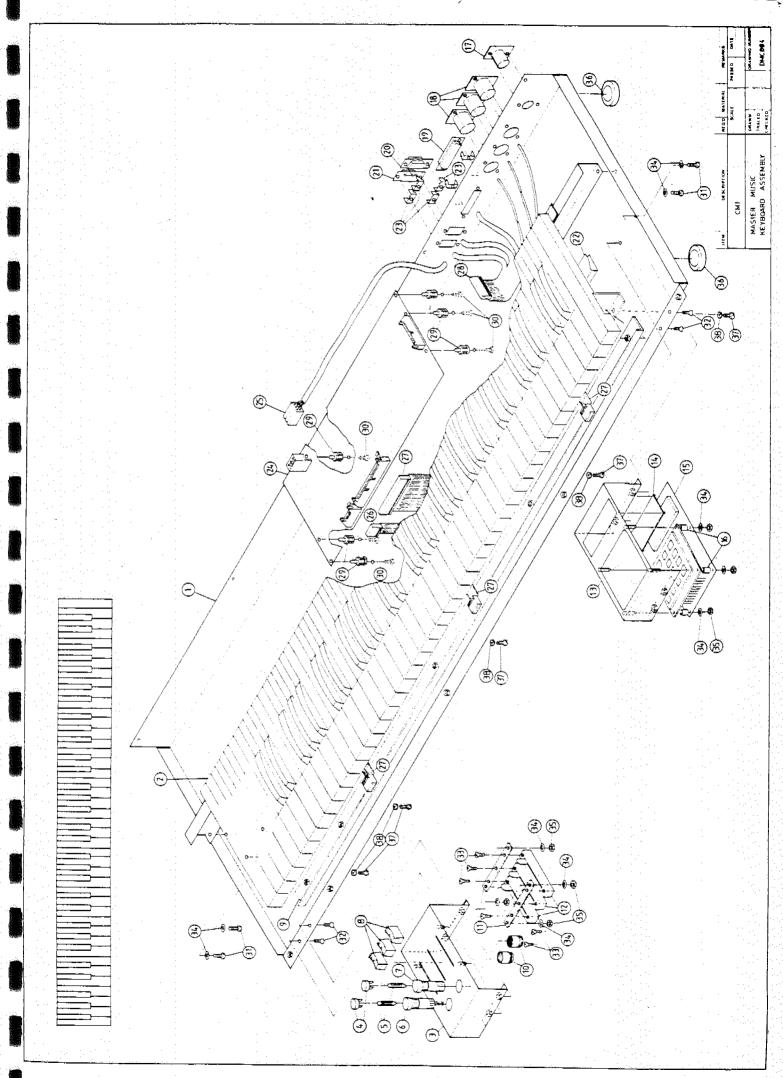

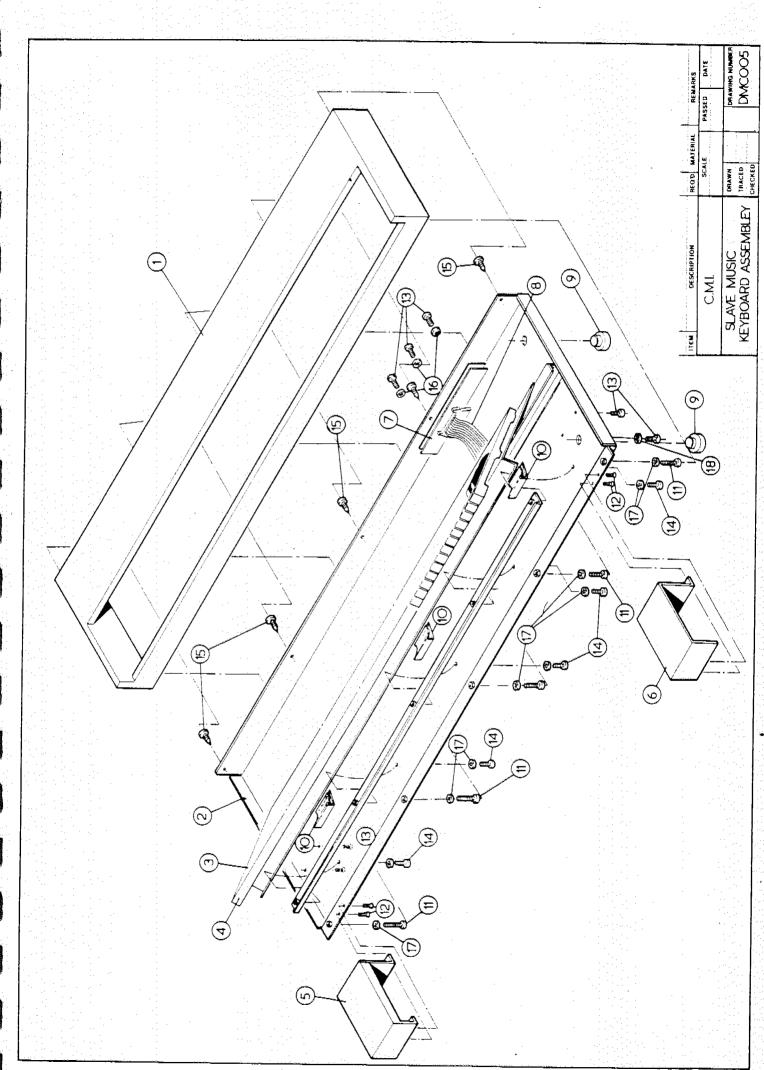

#### 2.3 MUSIC KEYBOARD

The music keyboard interfaces to the Mainframe via a bi-directional RS-232C port located on the processor control card Q-133. The Baud rate is selected by D.I.L. switches inside the keyboard. These must be set to 9600 Baud.

The keyboard is controlled by an on-card M6802 microprocessor executing a program in EPRCM. As well as data communications with the Mainframe, data coming in from the alpha-numeric keyboard is pre-processed before being forwarded to the mainframe.

# 2. FUNCTIONAL DESCRIPTION (continued)

Data is sent to the computer whenever:

- 1) A music key is depressed or released

- 2) A key on the alpha keyboard is pressed

- 3) One of the three faders is moved

- 4) A switch or pedal plugged into the keyboard is operated.

Keystroke data is sent in the form of three-byte packets. This includes keyboard number, key number, depression/release flag and key velocity data. Key velocity is calculated by the on-card processor which times the flight of the key contact as it travels between two busbars.

The 12 digit alpha-numeric display on the right-hand end of the keyboard is used to display messages to the operator in circumstances where the Graphics Terminal is not being used. The display is controlled by the processor on the keyboard. On power-up, the message - POWER ON - is displayed. This is generated locally by the keyboard itself. Once Booting has commenced, the message LOADING is displayed. This message is sent by the mainframe, via the serial link.

The control devices (faders, switches and pedals) are digitised by an eight-bit Analog to Digital converter in the music keyboard and when the data changes, a packet of data is transmitted down the serial link to the mainframe.

For detailed information, refer to the MUSIC KEYBOARD SERVICE MANUAL.

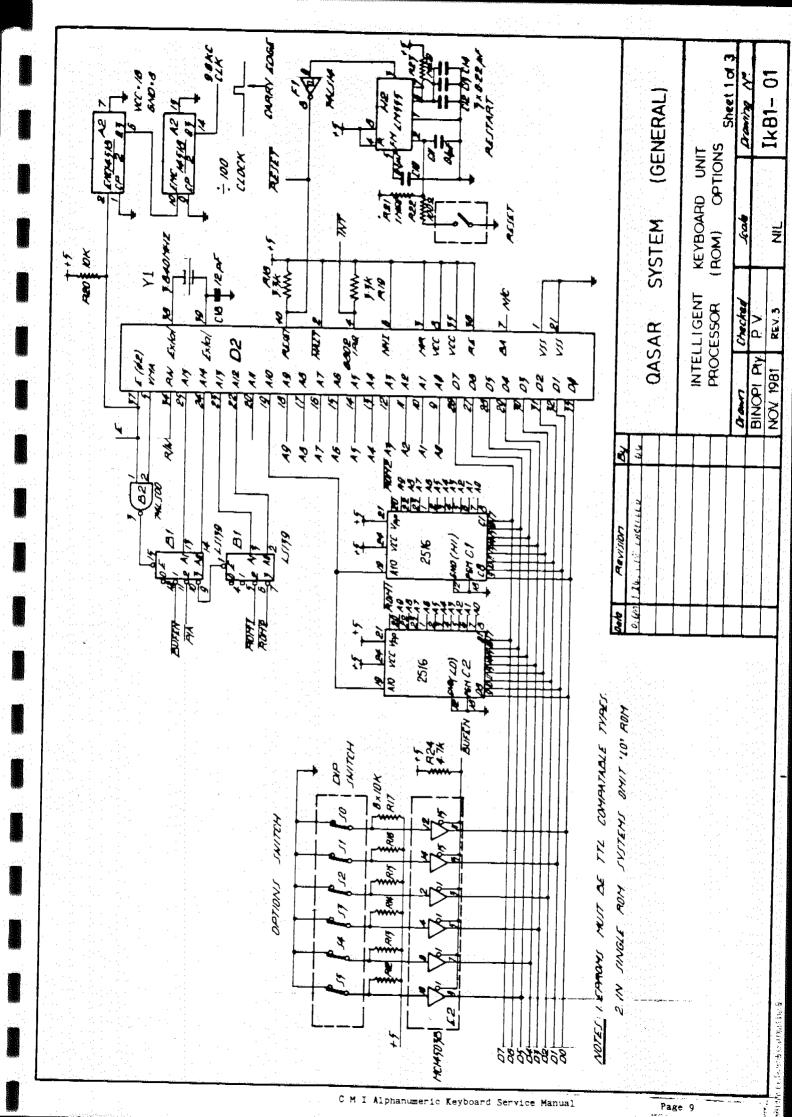

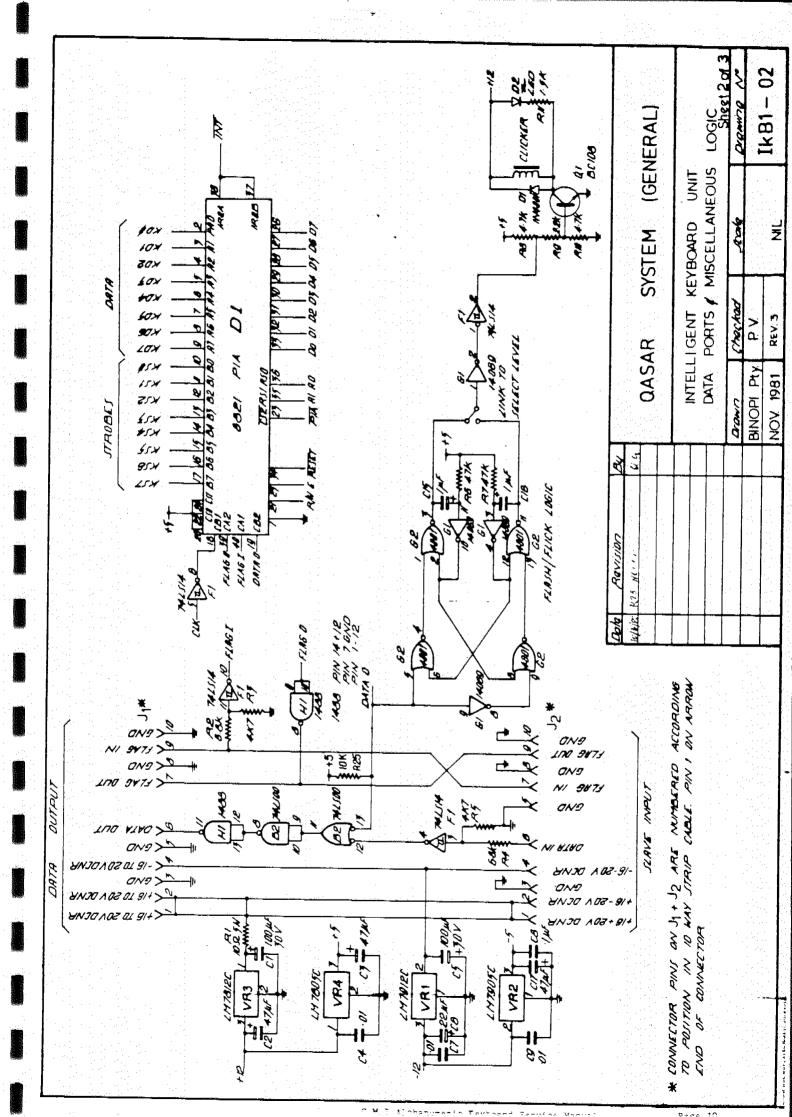

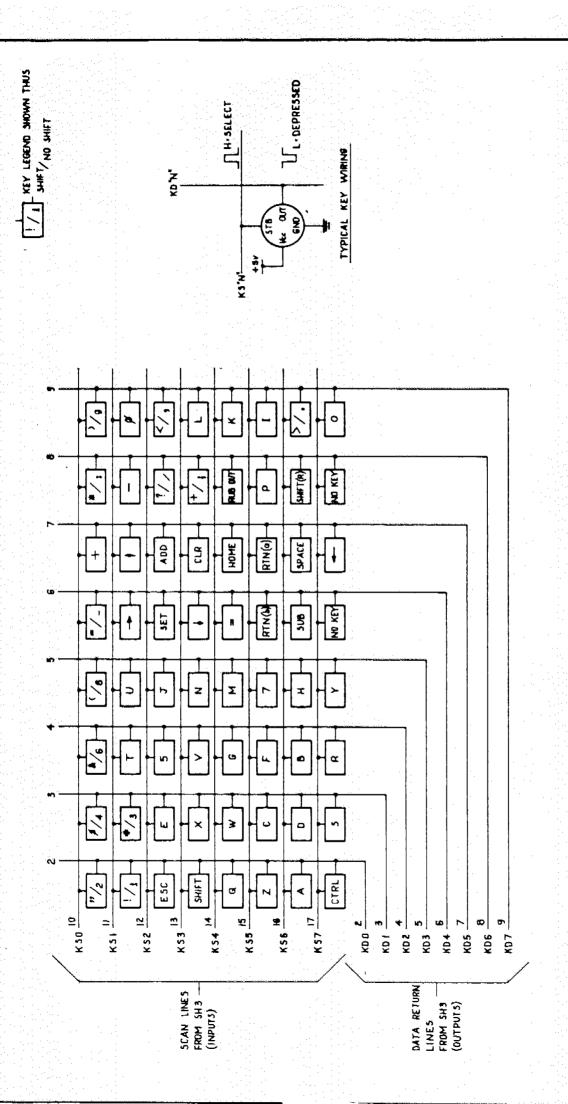

## 2.4 ALPHA-NUMERIC KEYBOARD

This keyboard uses another M6802 microprocessor which controls scanning of the 62 Hall-effect switches and serialises the data which is transmitted in ASCII format, RS-232C protocol. Data rate used is 9600 Baud, selected by D.I.L. switches on the circuit board. The processor executes firmware stored in EPROM.

Normally the alpha-numeric keyboard is plugged into the music keyboard. It receives its power from there, and sends its data to the processor in the music keyboard. The data is flagged as alpha-numeric, queued until there is no music keyboard data, and then forwarded to the mainframe. If desired, the alpha keyboard can be plugged directly into the Keyboard connector on the mainframe, bypassing the music keyboard. This can be a useful diagnostic aid.

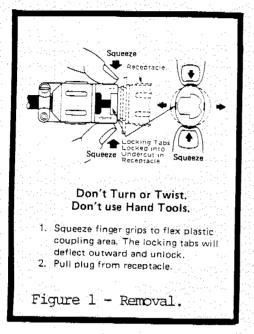

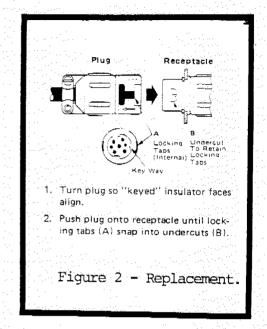

### 2.5 INTERCONNECTING CABLES

The four major sub-systems are connected by pluggable cable sets which should be treated with the same suspicion warranted by mechanical parts. The signals carried by each cable, together with pin numbers, are described fully in section 4, below.

#### 3. TROUBLESHOOTING

This section covers troubleshooting the C.M.I. system only to the level of identifying which of the four sub-systems (mainframe, music keyboard, alpha-keyboard or graphics terminal) is at fault. Having done this, service personnel should refer to the service manual for the offending item.

NOTE: Remember that the C.M.I. is a complex piece of hardware running sophisticated software, and it is sometimes hard to differentiate between a hardware fault, software bug, and operator error. If there is any doubt, the same sequence of operations should be tried on a known good system before attempting hardware repairs. In executing the following diagnostic procedures, the serviceperson should be aware that a faulty System Disk can cause what appears to be hardware faults. Furthermore, hardware faults can cause disks to be destroyed, either physically or by corrupting data, so it is wise to keep a good supply of C.M.I. system disks and diagnostic disks on hand.

### 3.1 SUB-SYSTEM SUBSTITUTION

The easiest way to identify the faulty sub-system is to exchange whole units for known good ones if such are available. If a complete working system is on hand, exchange each sub-system in turn, starting with the most likely to be responsible for a given fault. Some common fault symptoms and suggested substitution procedures follow.

3.1.1 System will not boot. Successful Boot is indicated by Page 1 appearing on the screen, or Page 1 Ready message at the music keyboard.

Unplug keyboard from mainframe. If it still does not boot, the fault is in the mainframe. If it does boot, try substituting the music keyboard. If it still does not boot, substitute the alpha-keyboard. The Graphics Terminal should not be able to affect booting. If the problem does not go away at any stage, substitute the interconnecting cables one by one.

3.1.2 System boots (Page 1 on screen or message at keyboard) but does not respond to alpha keyboard commands.

Substitute music keyboard, then alpha keyboard, then graphics terminal, then cables. If problem persists, the fault is in the mainframe.

3.1.3 No sound when voice loaded and music keyboard played.

Substitute music keyboard first, then cables, then alpha keyboard, then graphics terminal. If problem persists, the fault is in the mainframe.

3.1.4 System works properly except Graphics display or lightpen malfunctions.

Substitute graphics terminal and cable first. If no better, fault is almost certainly in mainframe.

3.1.5 Other strange behaviour.

Start by substituting mainframe.

# 3. TROUBLESHOOTING (continued)

# 3.2 SUB-SYSTEM CHECKOUT WITHOUT SUBSTITUTION

In many cases the faulty sub-system will have to be identified using only commonly available test equipment. Minimum requirements are a multimeter for measuring volts D.C. and resistance, an oscilloscope, and the usual set of tools such as screw drivers, pliers, soldering iron, etc.

The faulty sub-system can usually be isolated by the following tests:

3.2.1 System will not boot.

Unplug keyboard input and try again. If system does not boot, fault is in mainframe. If it now boots, fault is in music keyboard, alpha keyboard or cables. To isolate which, try again with alpha keyboard plugged straight into mainframe to eliminate music keyboard.

3.1.2 System boots but does not respond to alpha keyboard commands.

Most likely fault is in alpha-keyboard or cable. If the keyboard does not click when a key is pressed, either the keyboard is faulty or the power supply to the keyboard has failed. Check the supplies and data output at the keyboard plug using the Signal List. See Section 4.

3.1.3 No sound when voice loaded and music keyboard played.

Check for normal operation with the alpha-keyboard plugged directly into the mainframe. Check for correct signals at the power and signal connectors at the music keyboard. See Section 4.

# 3. TROUBLESHOOTING (continued)

3.1.4 System works properly except Graphics Terminal malfunctions.

Check video ouput signal at the Graphics connector. If this is normal, fault is in Graphics Terminal or cable. Note that a negative image can be caused by a fault in the graphics terminal or the mainframe, and cannot be easily seen by looking at the signal on an oscilloscope. To achieve a substantially black image for examination with the oscilloscope, remove the system disk and restart both processors. This will result in the words LOAD SYSTEM DISK IN DRIVE 1 on a black screen, in which case the scope display should show any fault clearly.

3.1.5 Lightpen does not work but everything else normal.

Point the lightpen at a light area of the screen. If there is a cursor which disappears when the Touch is activated, then the fault is in the mainframe. Otherwise the fault may be in the Graphics Terminal, lightpen or cables. Check for proper Hit and Touch signals at the Graphics connector at the mainframe by unplugging the cable and using an oscilloscope. If these are not correct the fault is in the Graphics Terminal. Otherwise the mainframe is faulty.

3.1.6 Other strange behaviour.

Most other faults such as improper operation of one or more of the sound channels or unreliable response from the computer can be attributed to a fault in the mainframe. To eliminate all other possibilities a useful diagnostic trick is to start the system playing a long Page R, Page C - M.C.L. or Page 9 Sequencer loop and un-plug all cables except the mains input and audio ouput. If the fault is still evident, then the mainframe is definitely to blame.

# 4. SIGNAL LISTS

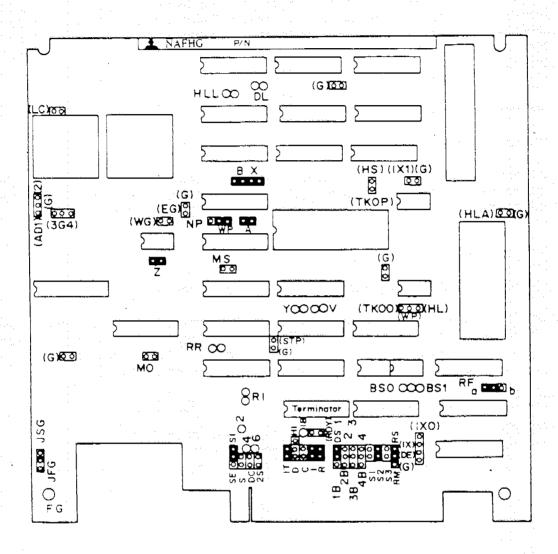

This section describes the signals present in each conductor of each interconnecting cable in the C.M.I. System when functioning normally. Refer to Figure 2 for cable identification.

Figure 2 C.M.I. SYSTEM INTERCONNECTION CABLES

- 4.1 Mains Cable: Part no. MC068 (I.E.C.)

- A.C. Mains Neutral, Active and Ground.

- 4.2 Graphics Terminal Power: Part no. MC067 (I.E.C.)

- A.C. Mains supply to Graphics Terminal. Switched by key switch on mainframe. This supply is always the same as the local mains potential.

- 4.3 Graphics Terminal Signal: MC065

Video signal to Graphics Terminal and Light Pen signals to mainframe. Connector Type: Cannon 5-pin.

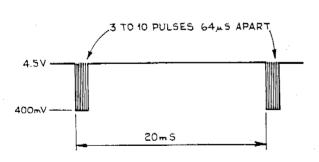

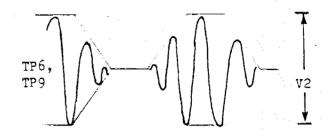

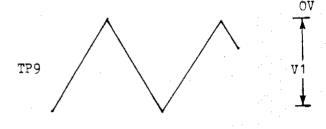

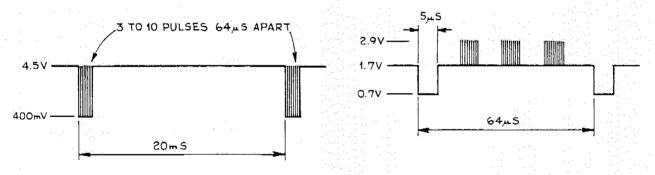

- Pin 1 Lightpen Hit. T.T.L. level, asserted low. On oscilloscope, appears as a series of low-going pulses about 1uS wide, repeated every 20mS, when the pen is pointed at a bright area of the screen. (See fig 3a)

- Pin 2 Lightpen Signal Return. Ground for lightpen signaal cables.

- Pin 3 Lightpen Touch. T.T.L. level, asserted low. Normally at approximately +4 volts, goes low (less than 0.4 V) when the end of the lightpen touched.

2.97

1.7V

- Pin 4 Video Return. Ground for Video signal cable.

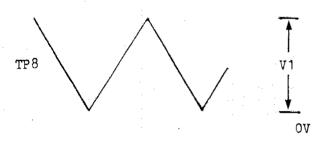

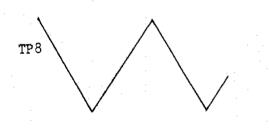

- Pin 5 Composite Video. 1V P-P video signal to Gr aphics display. Format is 625 lines, 50 Hz frame rate. See fig 3b.

0.7V 64,u.5

Figure 3a LIGHTPEN HIT SIGNAL

Figure 3b COMPOSITE VIDEO

## 4.4 Music Keyboard Power: MC064

Unregulated power supply to music keyboard. Also indirectly supplies alphanumeric keyboard.

Connector Type: Cannon 7-pin.

- Pins 1,2 +10V Return. Return (ground) for +10V supply.

- Pins 3,4 +10V Supply. Unregulated supply, +9 to +11 volts.

- Pin 5 -20V Supply. Unregulated supply, -18 to -22 volts.

- Pin 6 +20,-20 Return. Return (ground) for + and 20 supplies.

- Pin 7 +20V Supply. Unregulated supply, +18 to +22 volts.

# 4.5 Music Keyboard Signal: MC060

Bi-directional serial data between mainframe and music keyboard, including "busy" flags in both directions. Power supply is also carried by this cable, to power the alpha-numeric keyboard if it is connected instead of the music keyboard.

Connector Type: 9 Pin "D-Mini"

- Pin 1 +18 to 22 volts unregulated supply. This is not used by the music keyboard.

- Pin 2 DON1. Signal to enable transmission of data from the keyboard. RS-232C levels. Enabled: >7 volts. Disabled <-7 volts. With nothing being transmitted from the keyboard, this signal should be at approx. +10 volts. When keys are pressed or released a burst of -10 volt pulses should be seen for between 2 and 10 milliseconds.

- Pin 3 -18 to -22 volts unregulated supply. This is not used by the music keyboard.

- Pin 4 FLAG1. Signal to diasble transmission of data from the mainframe to the keyboard. Signal is normally +10 volts.

- Pin 5 SIGNAL RETURN. Ground for data paths.

- Pin 6 DATA IN. Serial data from keyboard to mainframe. Format is RS-232C. Normally at -10 volts. When a key is pressed or released a burst of +10 volt pulses lasting approx. 3 mS sholud be seen.

- Pin 7 POWER RETURN. Return (Ground) for + and supplies.

- Pin 8 Not Connected.

- Pin 9 DATA1. Serial data from mainframe to keyboard. Format is RS-232C. Normally at -10 volts. For each character sent from the mainframe to the alpha-numeric display a burst of +10 volt pulses lasting approx. 1 mS should be seen.

## 4.6 Alpha-numeric Keyboard Power/Signal: MC013

Unregulated power supplies to alphanumeric keyboard, serial data from alphanumeric keyboard.

Connector Type: 9 Pin "D-Mini"

- Pin 1 +18 to +22 volts unregulated supply.

- Pin 2 Not Connected.

- Pin 3 -18 to -22 volts unregulated supply.

- Pin 4 Not Connected.

- Pin 5 SIGNAL RETURN. Ground for data paths.

- Pin 6 DATA OUT. Serial data from keyboard. Format is RS-232C.

Normally at -10 volts. Each time a key is pressed a burst of +10 volt pulses lasting approx. 1 mS should be seen.

- Pin 7 POWER RETURN. Return (Ground) for + and supplies.

- Pin 8 Not Connected.

- Pin 9 Not Connected.

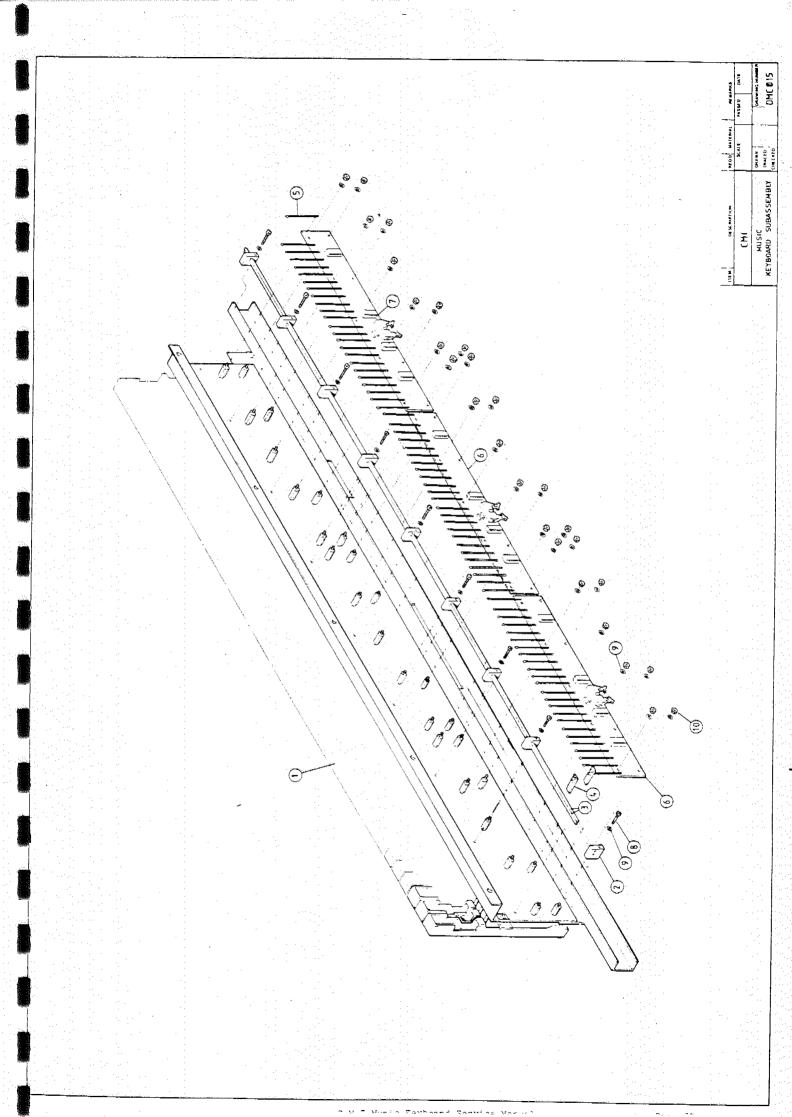

# 4.7 Slave Keyboard Power/Signal: MC059

The Music Keyboard sends power and key multiplexer addressing data to the slave keyboard. Key data is returned from the slave keyboard.

Connector Type: "D Mini" 25-pin.

- Pins 1,2 POWER SUPPLY RETURN. Ground.

- Pin 3 KEY ADDRESS O Least significant key multiplexer address bit.

- Pins 4,7 KEY ADDRESS BITS 1-4

- Pin 8 SIGNAL RETURN Ground.

- Pin 9 KEY DATA 1. Data returned from key multiplexer scanning the lowest 24 keys. Normally at approx. -5 volts. Goes to 0 volts while key is in flight, and +5 volts when key is at rest in fully depressed position.

- Pin 10 KEY DATA 2. Data from middle 24 keys.

- Pin 11 KEY DATA 3. Data from top 25 keys.

- Pins 11-21 Not Connected

- Pins 22,23 -20 SUPPLY. Unregulated power supply to slave keyboard, +18 to +22 volts.

- Pins 24,25 +20 SUPPLY. Unregulated power supply to slave keyboard, -18 to 22 volts.

### 4.8 Printer: MC062

Serial data from mainframe to optional printer, "busy" flag from printer to mainframe, plus "device on" signal used to switch on printer in readiness to receive data.

Connector type: Cannon 5 pin.

- Pin 1 Signal Ground.

- Pin 2 Not Connected.

- Pin 3 FLAGO. "Busy" flag from printer. RS-232C levels. <-7 volts when printer ready, >+7 volts when printer busy.

- Pin 4 DONO. "Device On" control from mainframe to printer. RS-232C level, >+7 volts to enable printer, <-7 volts to diable printer. This signal is optional as some printers do not require it.

- Pin 5 DATAO. Serial data to printer. RS-232C levels, ASCII format. Normally at -10 volts. For each character sent from the mainframe to the printer a burst of +10 volt pulses lasting approx. 1 mS should be seen.

#### 4.9 Phones

Output for driving headphones. Monitors the MIXED LINE output. Internally, this output is taken from the MONITOR (speaker) output via a 100 ohm resistor.

Connector type: 1/4" (6.25 MM) stereo phono jack.

The following signal lists refer to connectors on the rear of the C.M.I. Mainframe.

#### 4.10 Monitor

Output for driving a monitor speaker. The internal monitor amplifier will deliver a maximum of 20 watts R.M.S. into an 8 ohm speaker. Note that the Mainframe is fitted with a 1 amp speaker fuse which will blow if the monitor amplifier is driven to full output under load for more than a second.

Connector Type: Cannon 3 pin.

Pins 1,2 Ground

Pin 3 Active. With all channels producing a full-amplitude sinewave and the MONITOR control turned up to the point of clipping, this output should be approx. 38 volts P-P (with no load).

### 4.11 Channels 1-8

Individual channel outputs (balanced, 600 ohms impedance).

Connector type: Cannon 3 pin.

Pin 1 Ground

Pin 2 Output Cold. Anti-phase output, maximum level 3.7 volts P-P.

Pin 3 Output Hot. Maximum level 3.7 volts P-P.

#### 4.12 Mixed Line Output

Mixed output of all eight channels (balanced, 600 ohms impedance).

Connector Type: Cannon 3-Pin

Pin 1 Ground

Pin 2 Output Cold. Anti-phase output, maximum level 3.7 volts P-P.

Pin 3 Output Hot. Maximum level 3.7 volts P-P.

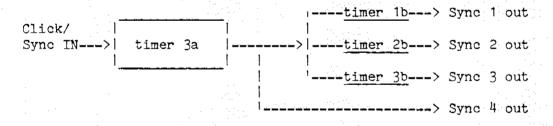

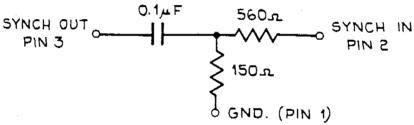

## 4.13 Sync

Synchronising input and output, for use with Real-Time Composer (Page R), Music Composition Language (Page C) or Keyboard Sequencer (Page 9). This connector serves as both an input and ouput.

Connector type: Cannon 3-pin.

- Pin 1 GROUND

- Pin 2 Sync Input. Pulses or tone of 1 to 20 volts P-P. Waveform unimportant. Frequency range 2 Hz to 5 kHz. Impedance 10 K ohms.

- Pin 3 Click Output. Periodic pulse, rate controlled by Page R R.T.C., Page 9 Keyboard Sequencer or Page C M.C.L. Waveform is a spike of approx. 5 volts peak, approx. 5 mS wide, alternately positive and negative going.

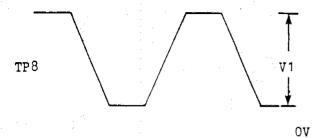

## 4.14 Filter Output

Output of the bandpass filter used by the Analog to Digital converter. It is designed to enable the operator to monitor the effect of various bandpass filter settings.

Connector type: Cannon 3-pin.

Pin 1 GROUND

Pin 2 GROUND

Pin 3 OUTPUT. Amplitude for full-scale conversion is 10 volts P-P. Source impedance 600 ohms.

## 4.15 Mic In

Balanced, 600 ohms input suitable for high output dynamic or condenser microphones. When the MIC/LINE switch is in the MIC position, this input is fed to the Analog to Digital converter.

Connector Type: Cannon 3-pin

Pin 1 GROUND

Pin 2 INPUT A

Pin 3 INPUT B

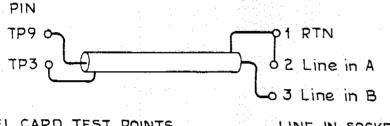

## 4.16 Line In

Balanced, 600 ohm line level input. This input is connected to the Analog to Digital converter when the MIC/LINE switch is in the LINE position.

Connector Type: Cannon 3-pin

Pin 1 GROUND

Pin 2 INPUT A. Amplitude of 1.4 volts P-P required for full scale conversion.

Pin 3 INPUT B. Amplitude of 1.4 volts P-P required for full scale conversion.

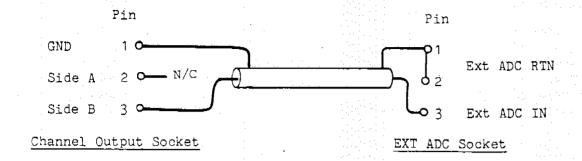

#### 4.17 ADC DIRECT

Direct input to the Analog to Digital converter when the ADC DIRECT/MIC LINE switch is in the ADC DIRECT position. Because this input is Direct Coupled, any D.C. offset on this input will result in a D.C. shift of a sound sample.

Connector Type: Cannon 3-pin-

Pin 1 GROUND

Pin 2 GROUND

Pin 3 INPUT. Amplitude for full scale conversion is 10 volts P-P.

### 5. REPAIR PROCEDURE

Having isolated the faulty sub-assembly, service personnel should refer to the relevant service manual for further details about that item.

### 6. PREVENTATIVE MAINTENANCE

Under normal conditions, the only preventative maintenance required for the C.M.I. is periodical cleaning of the mesh above the blowers in the Mainframe. Refer to the C.M.I. Mainframe Service Manual for full details.

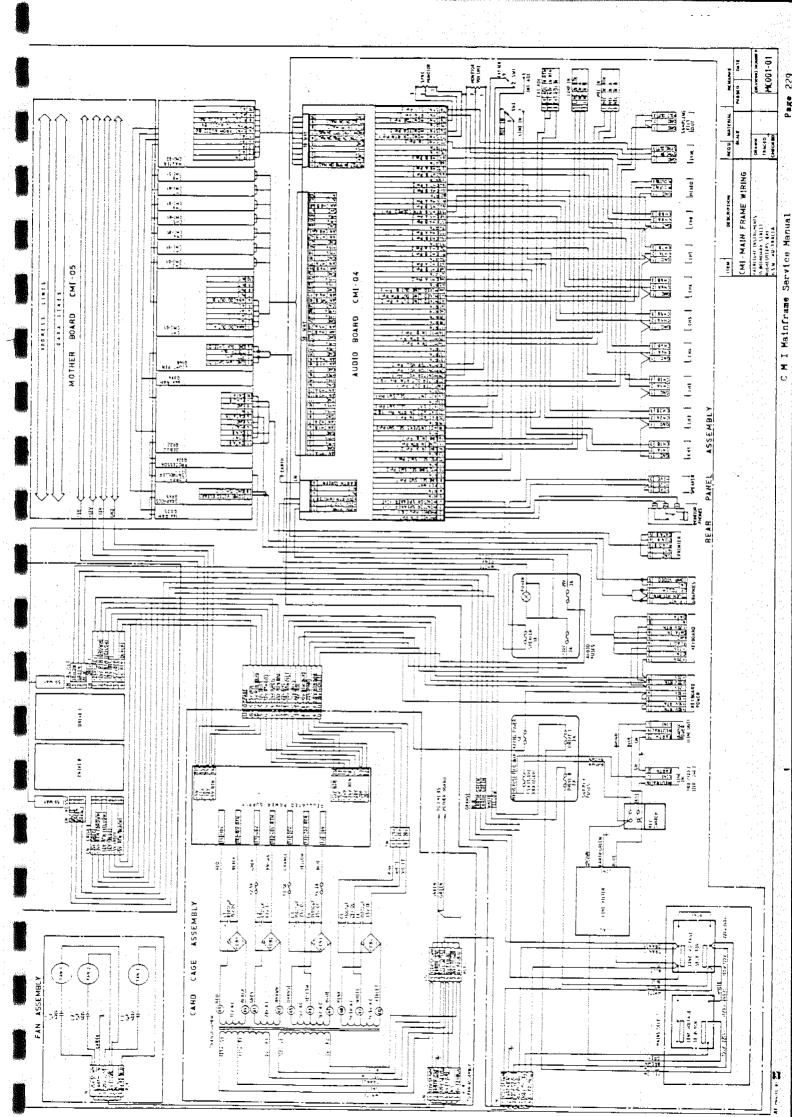

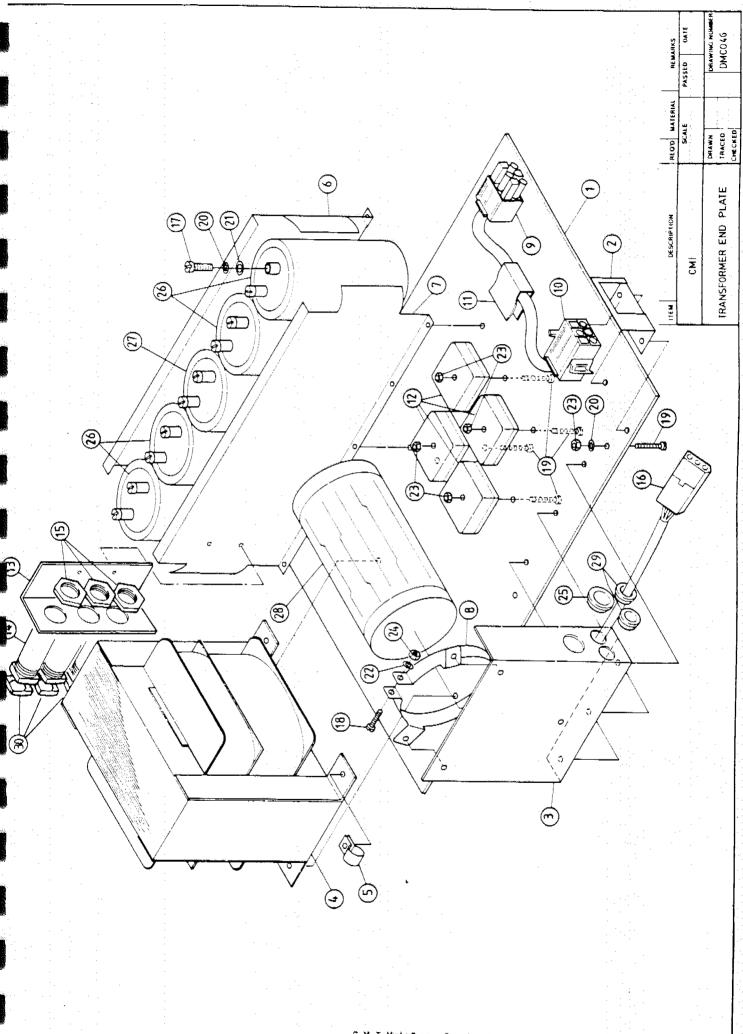

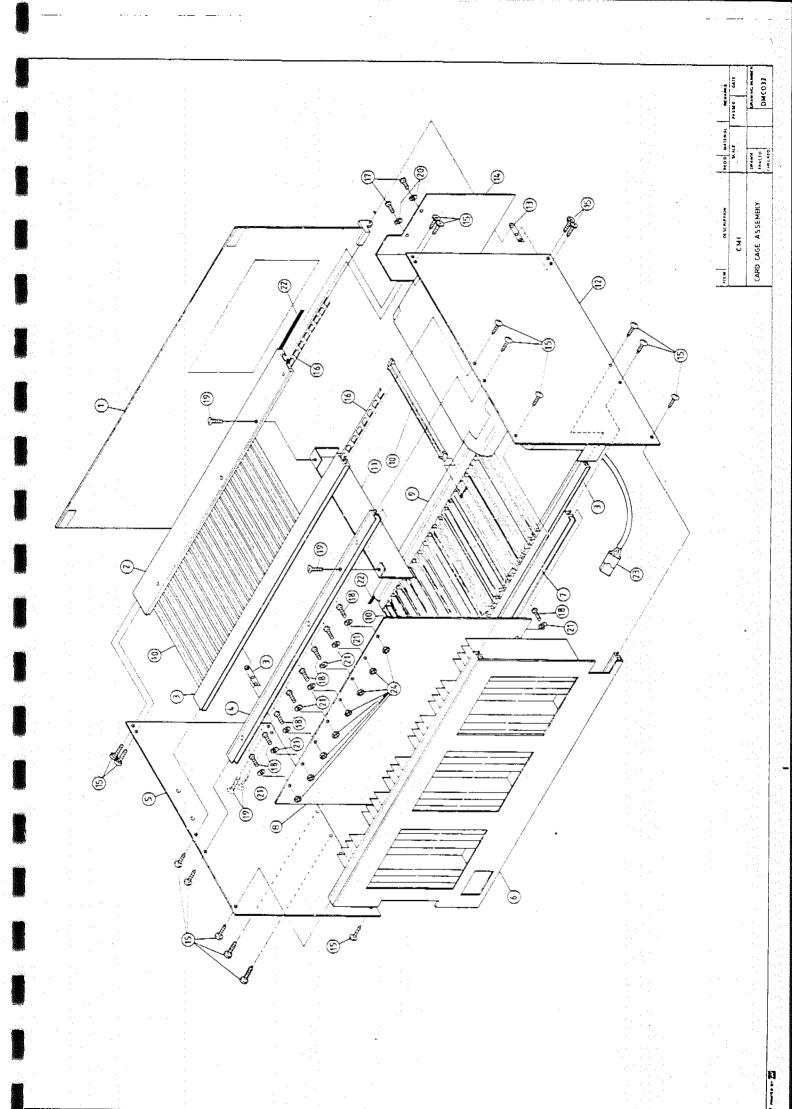

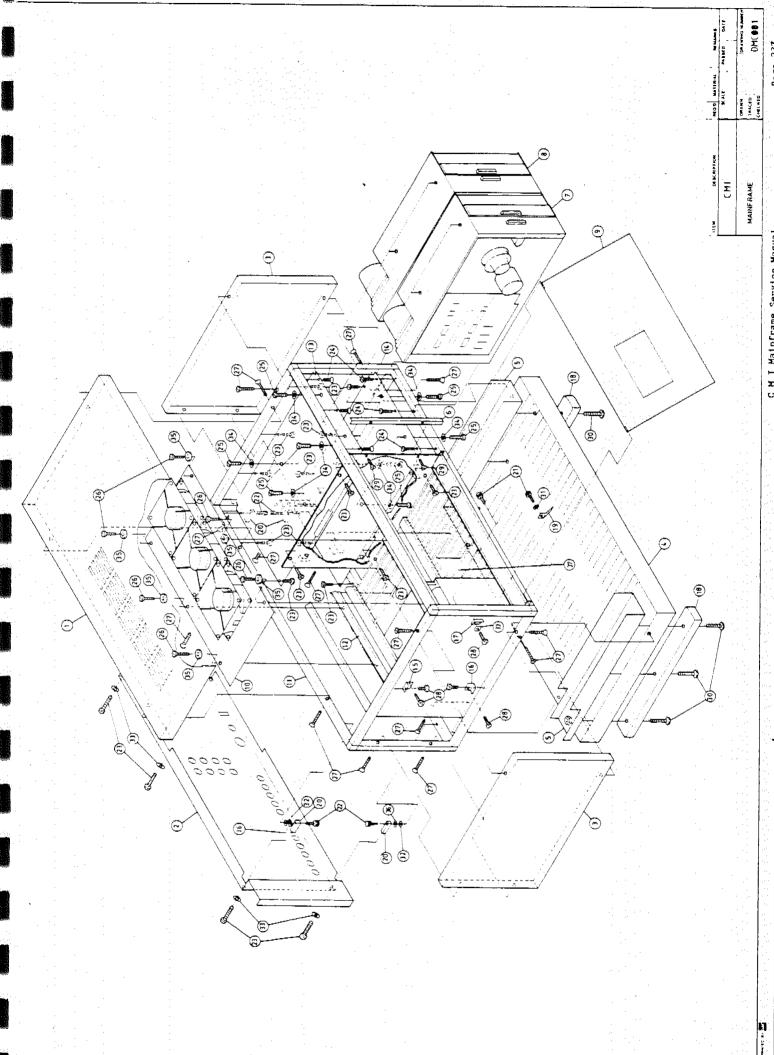

# C.M.I. MAINFRAME - #MC001

SERVICE MANUAL

FAIRLIGHT INSTRUMENTS - FEBRUARY 1985

Revision 2.1

## TABLE OF CONTENTS

|    |                                                | Page |

|----|------------------------------------------------|------|

| 1. | INTRODUCTION                                   | 1    |

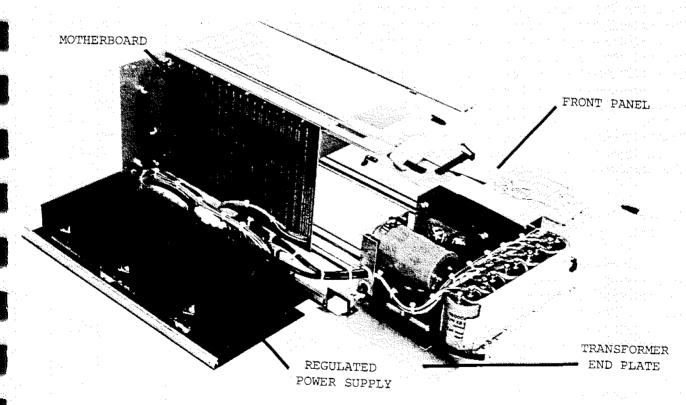

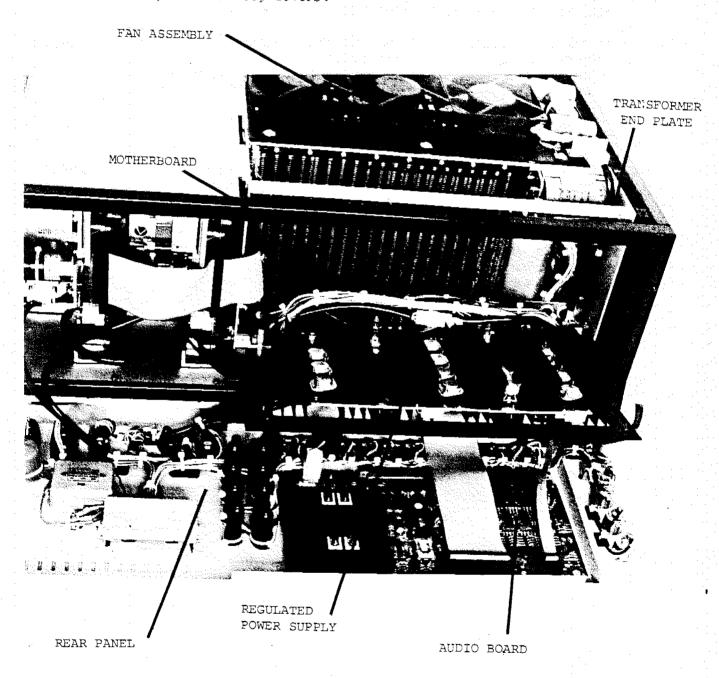

|    | 1.1 Card Cage                                  | 1    |

|    | 1.2 Audio Board                                | 1    |

|    | 1.3 Power Supply                               | 1    |

|    | 1.4 Floppy-Disk Drives                         |      |

|    |                                                | 1    |

|    | 1.5 External Connections                       | 2    |

|    | Figure 1. C.M.I. Mainframe Block Diagram       | 3    |

|    |                                                |      |

| 2. | SYSTEM OVERVIEW                                | 4    |

|    | 2.1 General Principles                         | 4    |

|    | 2.2 Hardware/Software Relationships            | 5    |

|    | 2.2.1 System Startup/Boot                      | 5    |

|    | 2.2.2 Disk Operations                          |      |

|    | 2.2.3 Lightpen/Graphics Display                | 6    |

|    |                                                |      |

|    | 2.2.4 Command Entry                            | . 6  |

|    | 2.2.5 Loading/Saving Sounds                    | 6    |

|    | 2.2.6 Sound Sampling                           | 7    |

|    | 2.2.7 Music Playing                            | . 7  |

|    | 2.2.8 Music Keyboard Functions                 | . 8  |

|    | 2.2.9 Keyboard Sequencer                       | 8    |

|    | 2.2.10 Music Composition Language              | 9    |

|    |                                                |      |

| 3. | SPECIFICATIONS                                 | 10   |

| ٠. | 3.1 ELECTRICAL                                 | 10   |

|    | 3.2 AUDIO                                      |      |

|    |                                                | 10   |

|    | 3-3 DIGITAL                                    | 11   |

|    | 3.4 MECHANICAL                                 | 11   |

|    |                                                |      |

| 4. | FUNCTIONAL DESCRIPTION                         | 12   |

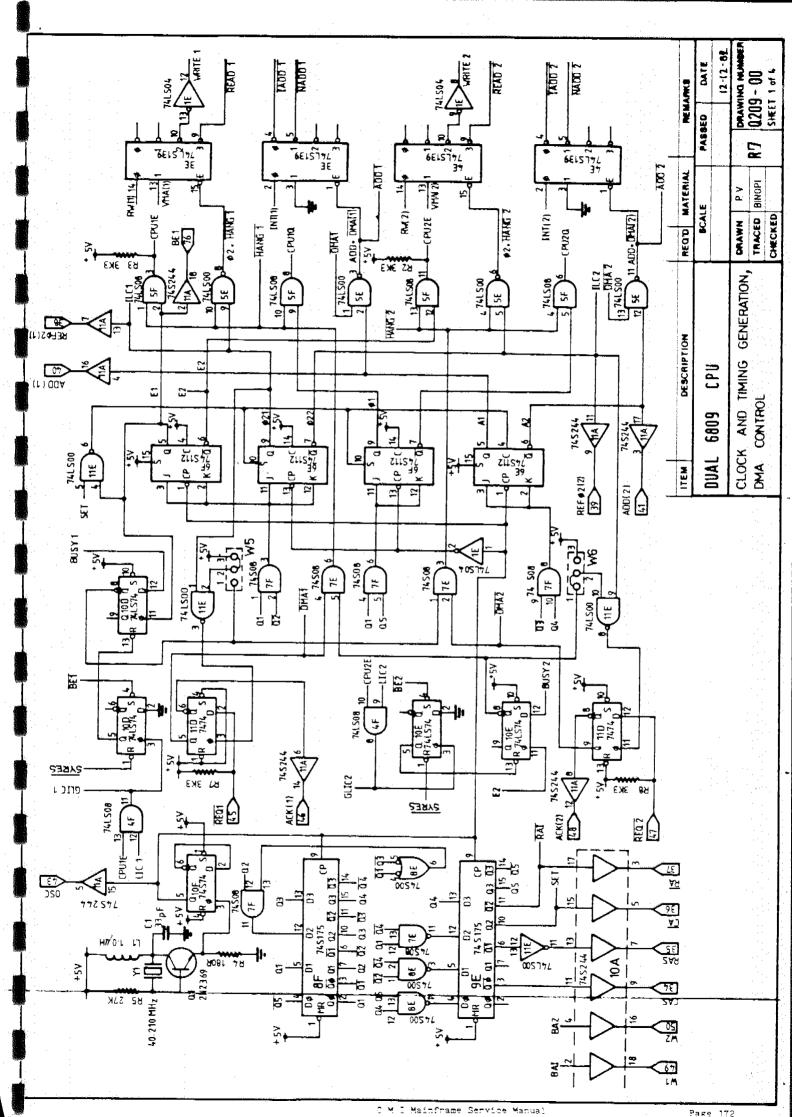

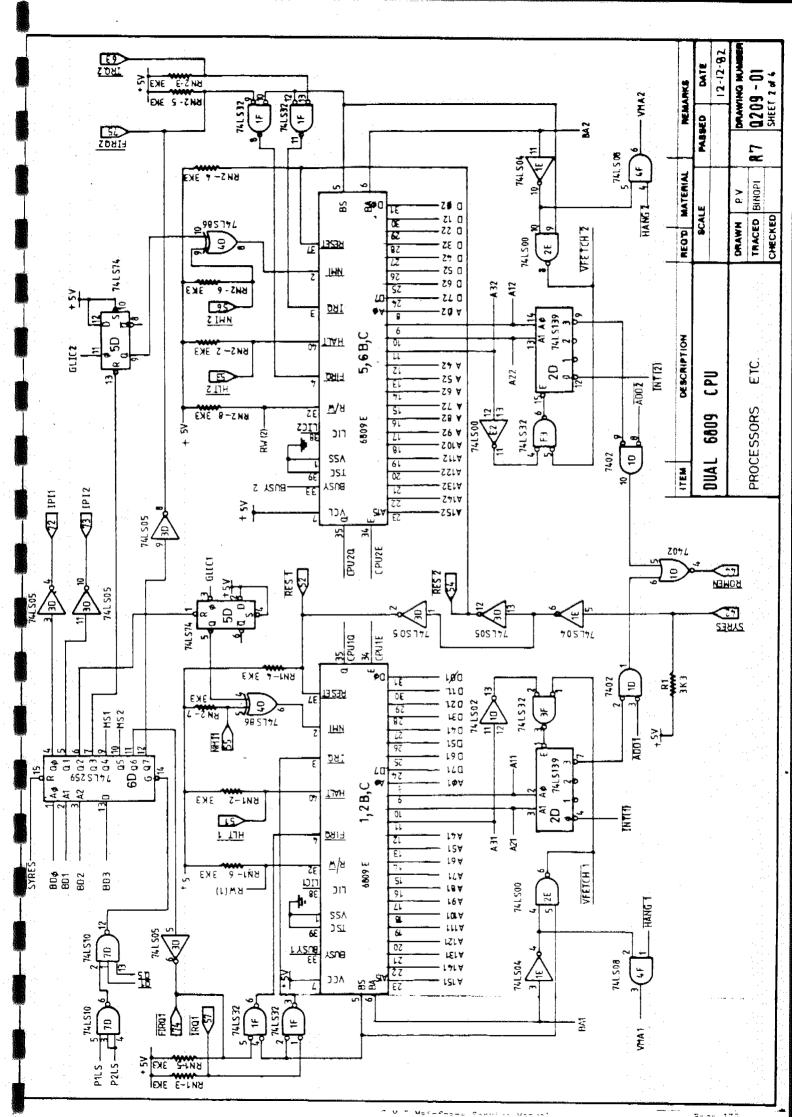

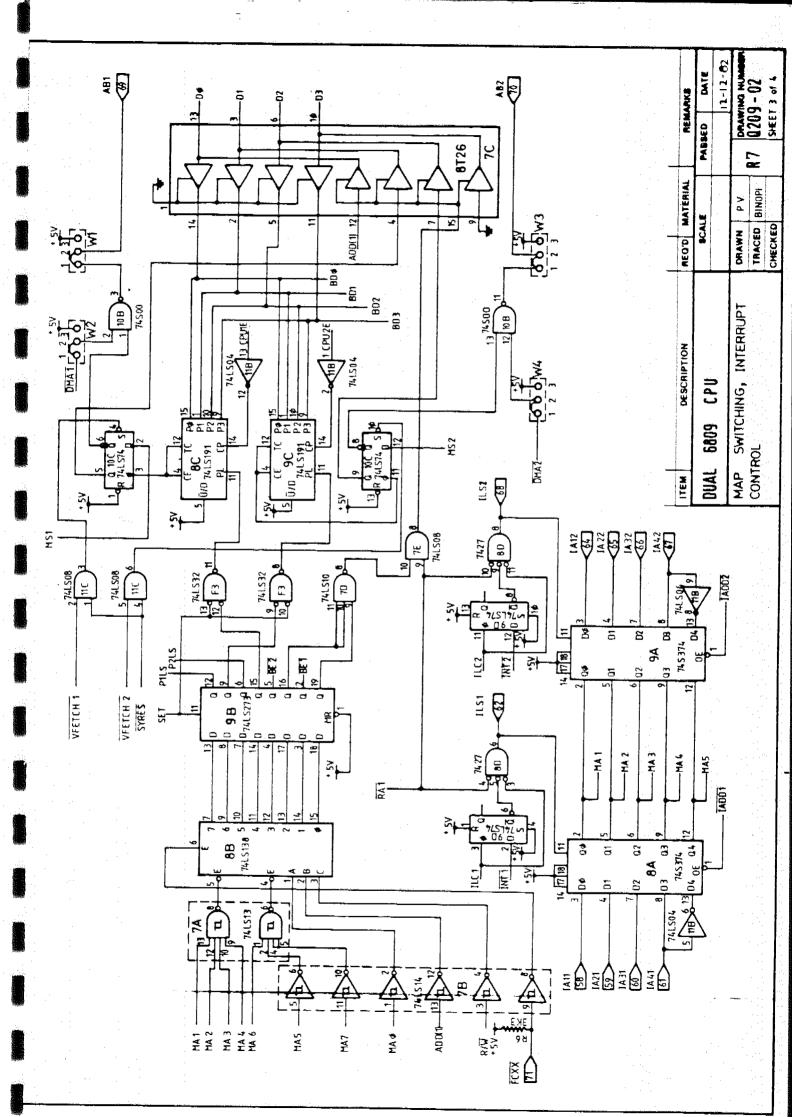

|    | 4.1 Q-209 DUAL 6809 CPU FUNCTIONAL DESCRIPTION | 12   |

|    | 4.1.1 INTRODUCTION                             | 12   |

|    | 4.1.2 TIMING & MEMORY CONTROL LOGIC            | 12   |

|    | 4.1.2.1 Master Timing Signals                  | 12   |

|    | 4.1.2.2 Dynamic Memory Timing Signals          | 12   |

|    | 4.1.2.3 Data, Address Buss Multiplexing        | 13   |

|    | 4.1.2.4 Interrupt Strobe Generation            |      |

|    | · ·                                            | 13   |

|    | 4.1.2.5 Direct Memory Access                   | 13   |

|    | 4.1.3 CPU MEMORY SWITCHING, & VECTORS          | 14   |

|    | 4.1.3.1 Vector-Fetch Decoders                  | 14   |

|    | 4.1.3.2 Processor System Control               | 14   |

|    | 4.1.3.3 Automatic Map Switching                | 15   |

|    | 4.1.3.4 Hardware Trace                         | 15   |

|    | 4.1.3.5 Indivisable Instructions               | 16   |

|    | 4.1.3.6 Link Options                           | 16   |

|    | · · · · · · · · · · · · · · · · · · ·          | 1.0  |

|     |                                                 | Page |

|-----|-------------------------------------------------|------|

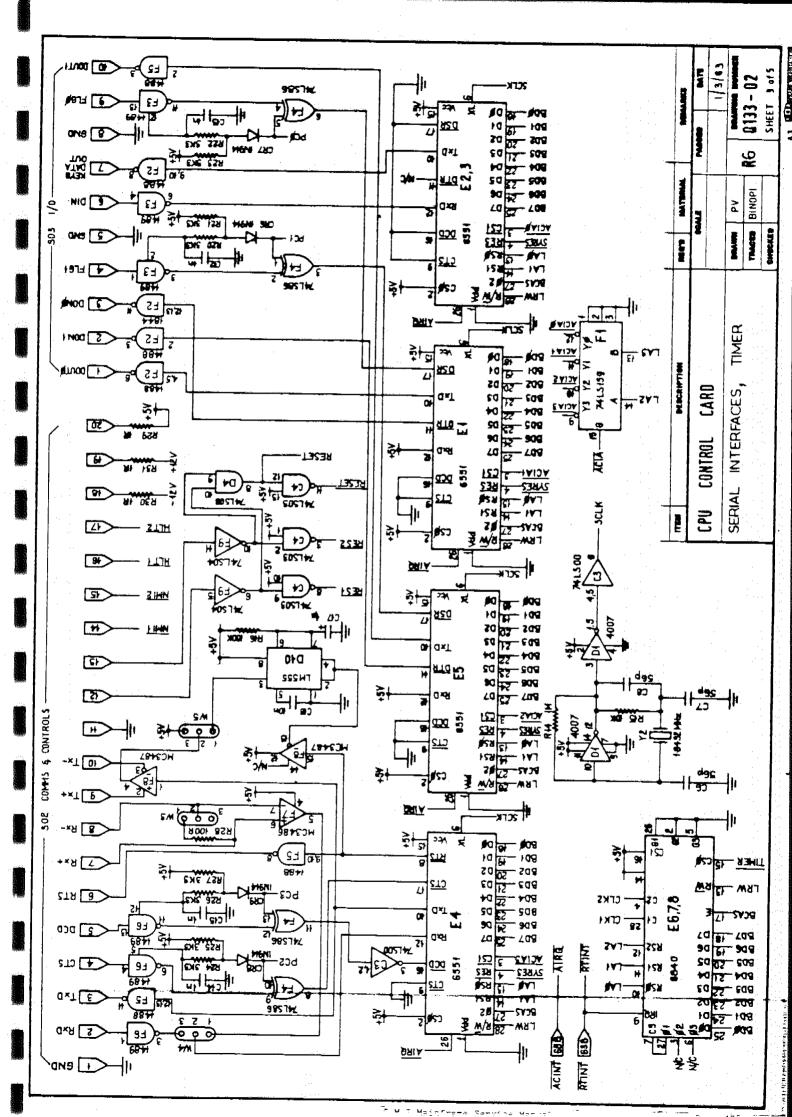

| 4.2 | Q133 CPU CONTROL CARD FUNCTIONAL DESCRIPTION    | 17   |

|     | 4.2.1 INTRODUCTION                              | 17   |

|     | 4.2.1.1 Address Map                             | 17   |

|     | 4.2.1.2 Restart and Interrupt Vectors           | 17   |

|     | 4.2.1.3 Debug Monitor ROM                       | . 18 |

|     | 4.2.1.4 System Boot/Disk ROM                    | 19   |

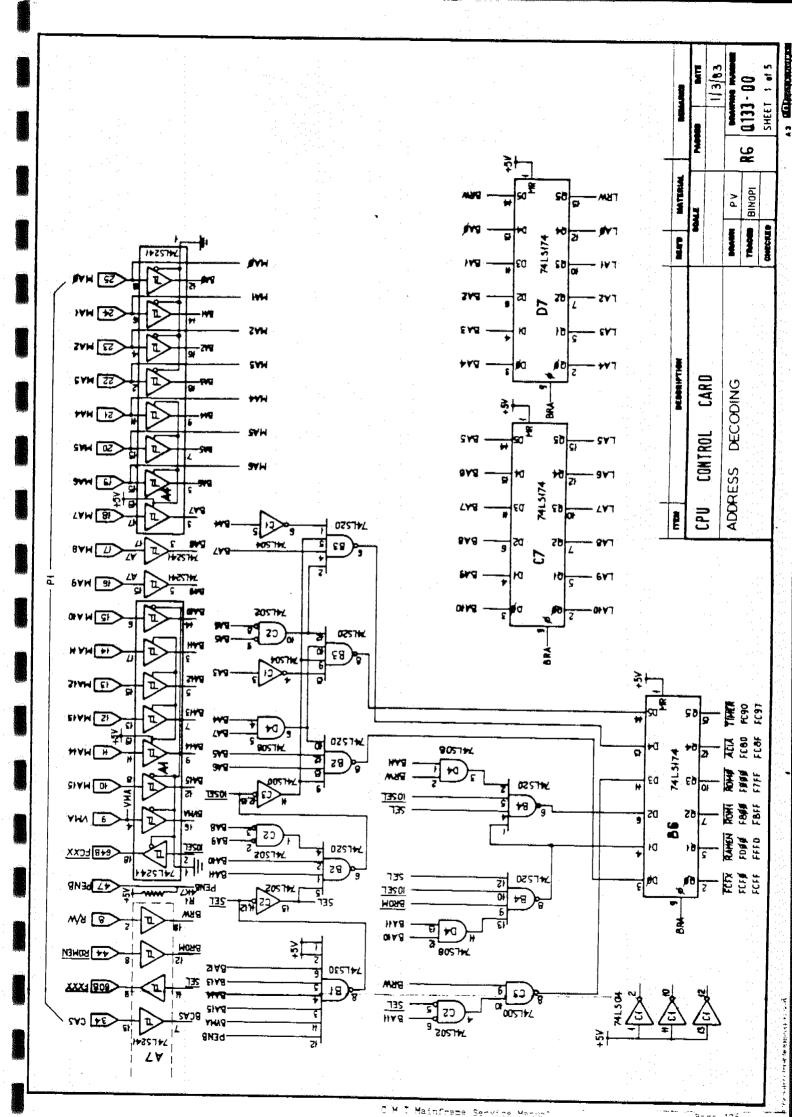

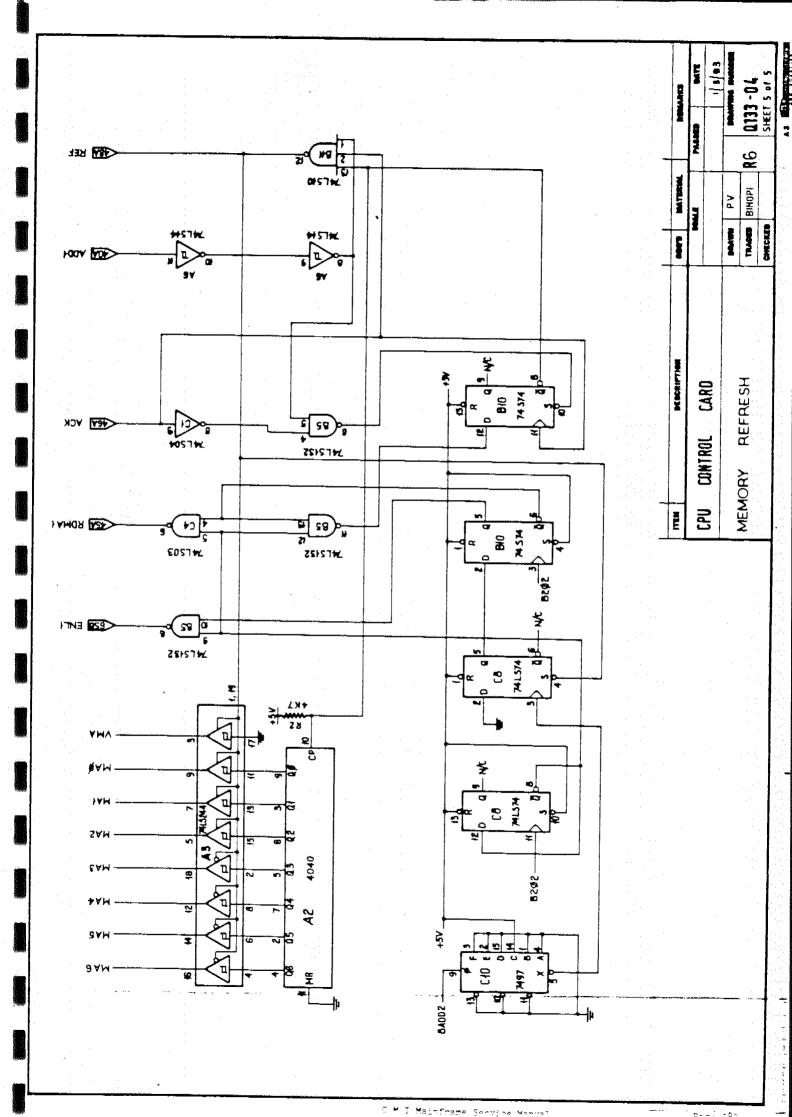

|     | 4.2.2 ADDRESS DECODING & RAM REFRESH CONTROL    | 20   |

|     | 4.2.2.1 Address Decoding                        | 20   |

|     | 4.2.2.2 RAM Refresh Control                     | 20   |

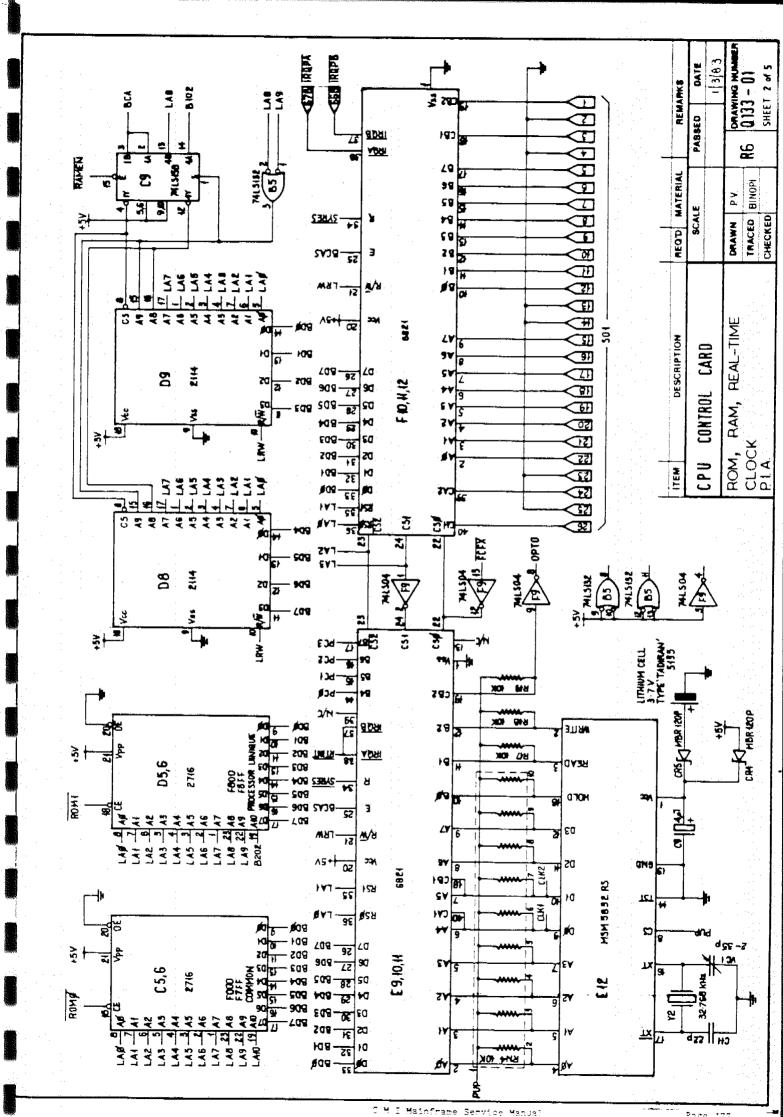

|     | 4.2.3 EPROM, RAM, ACIA, PIA                     | 21   |

|     | 4.2.3.1 Static RAM                              | 21   |

|     | 4.2.3.2 EPROM                                   | 21   |

|     | 4.2.3.3 ACIA                                    | 21   |

|     | 4.2.3.4 PIA                                     | 22   |

|     | 4.2.4 MANUAL CONTROLS, POWER-ON RESET           | 22   |

|     | 4.2.4.1 Manual Controls                         | 22   |

|     | 4.2.4.2 Power-on Reset                          | 22   |

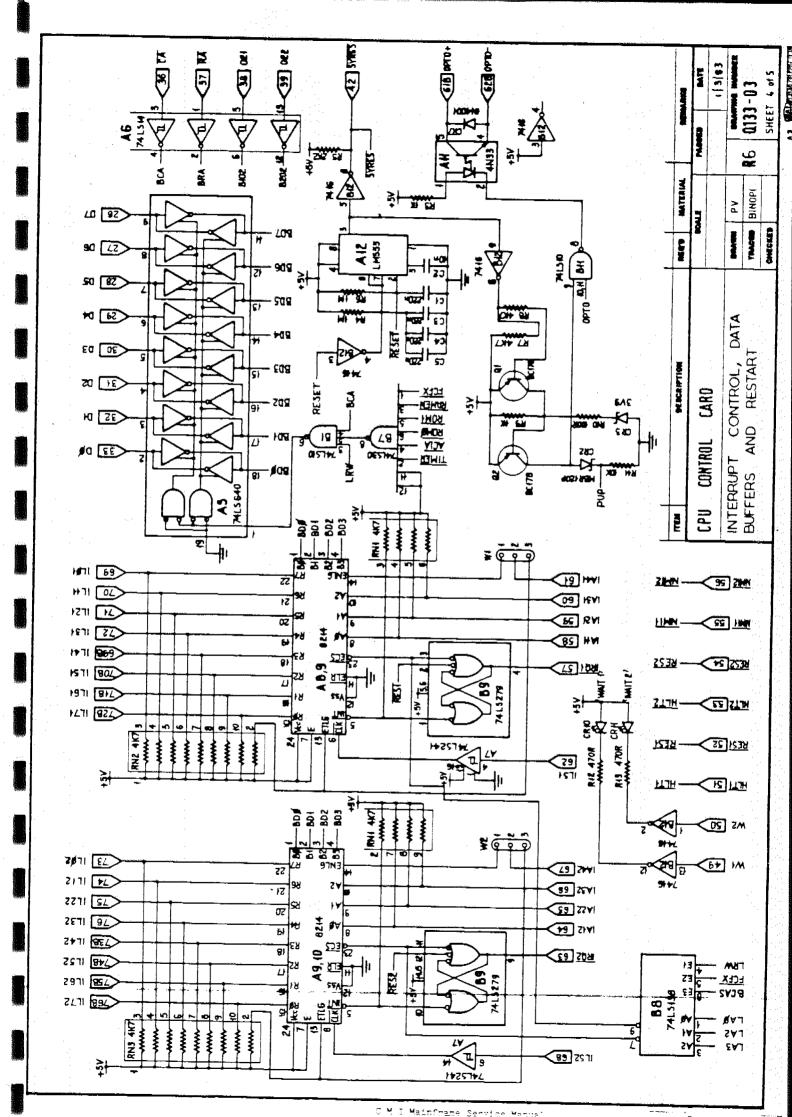

|     | 4.2.5 INTERRUPT PRIORITY LOGIC & DATA BUFFERS   | 23   |

|     | 4.2.5.1 Interrupt Priority Logic                | 23   |

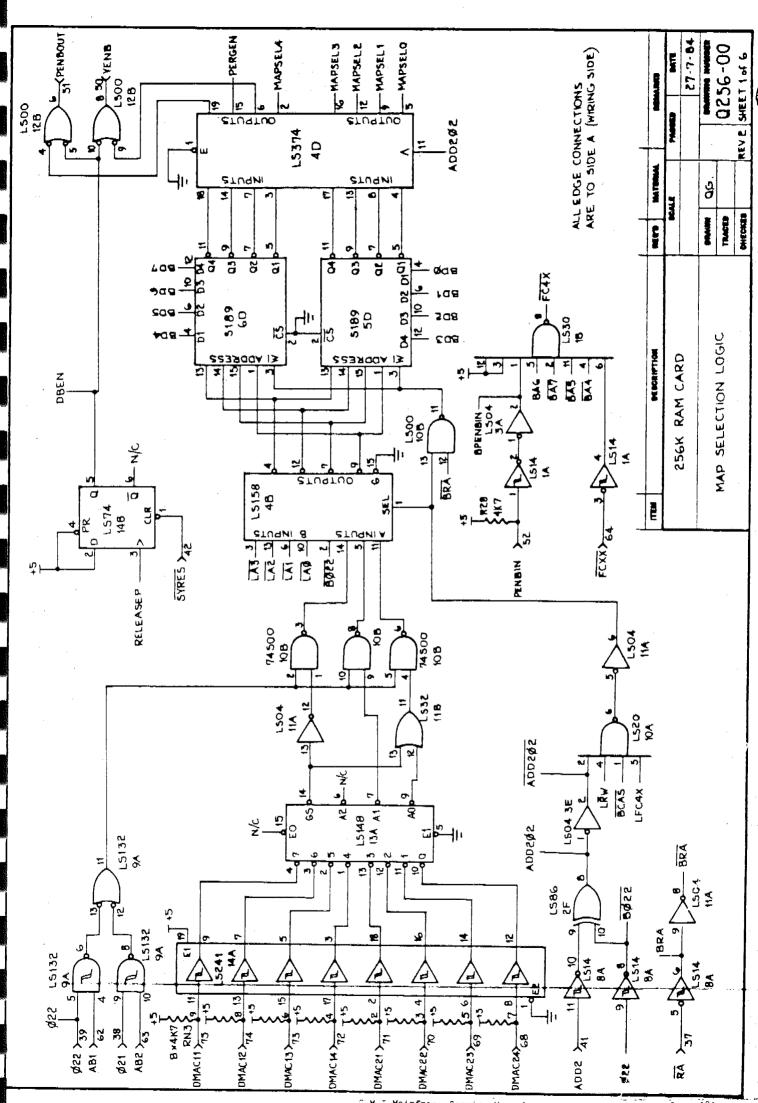

| 4.3 | Q-256 256K RAM CARD FUNCTIONAL DESCRIPTION      | 24   |

|     | 4.3.1 INTRODUCTION                              | 24   |

|     | 4.3.1.1 Options                                 | 24   |

|     | 4.3.2 ADDRESS DECODING & MAPPING LOGIC          | 25   |

|     | 4.3.2.1 Map Selection Logic                     | 25   |

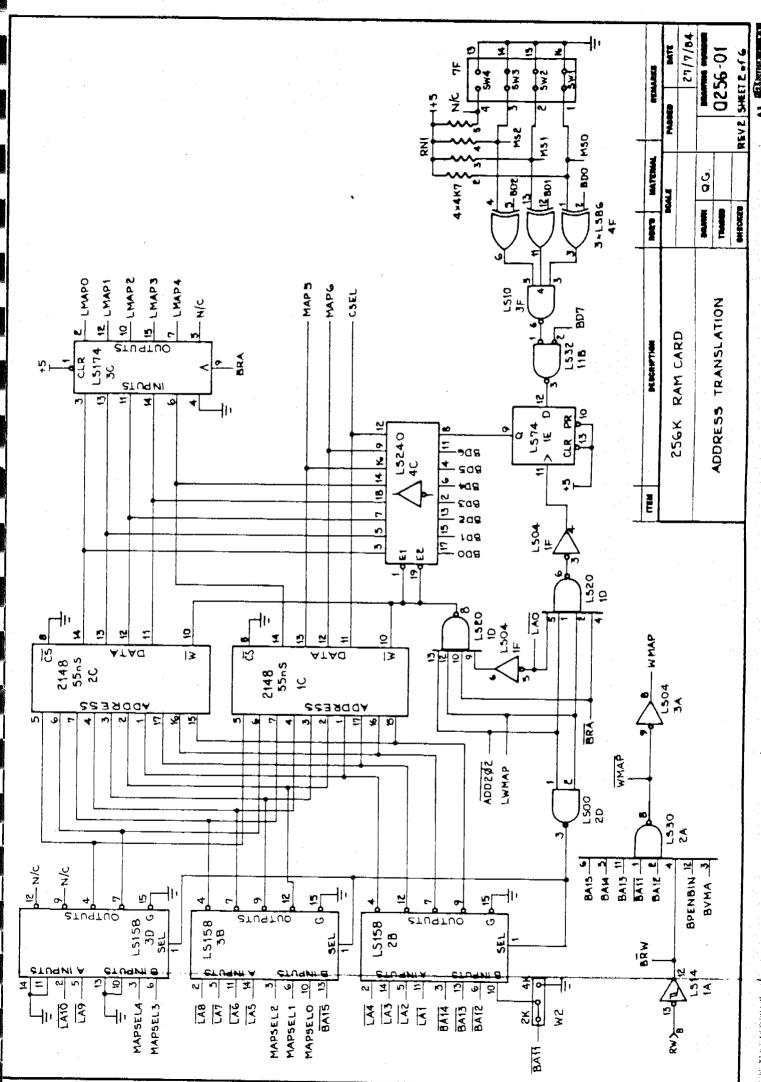

|     | 4.3.2.2 Address Translation                     | 27   |

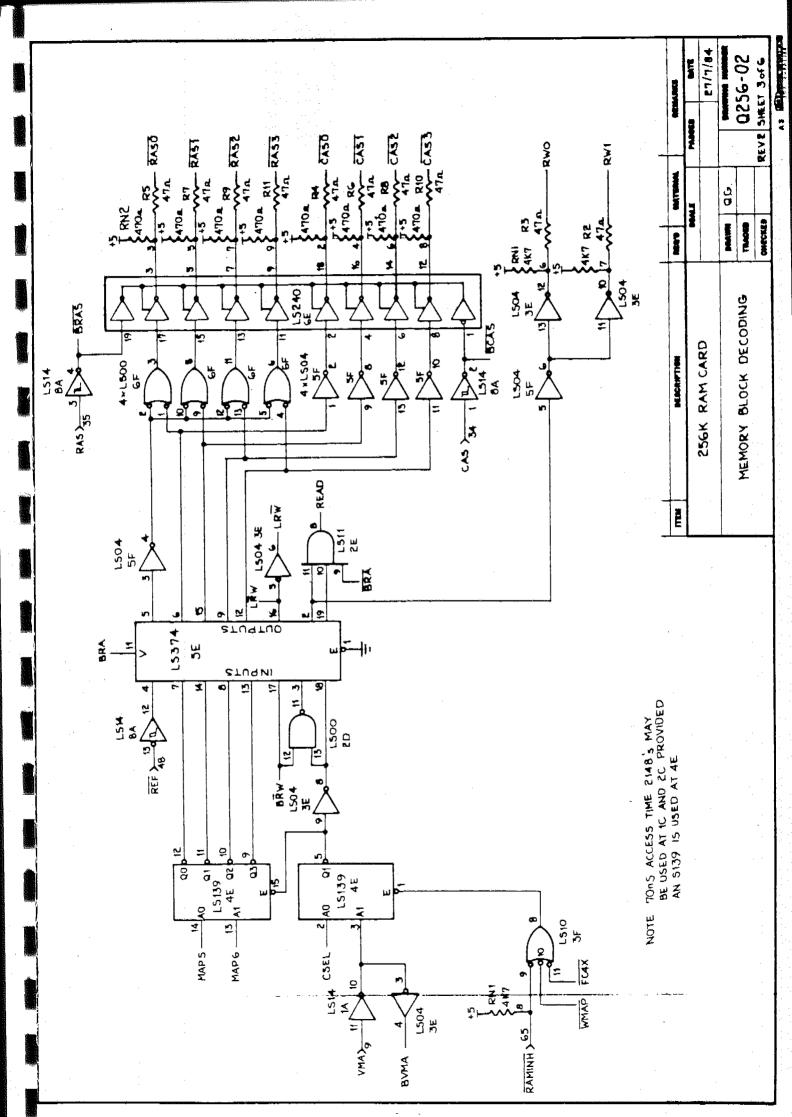

|     | 4.3.2.3 Memory Block Decoding                   | 28   |

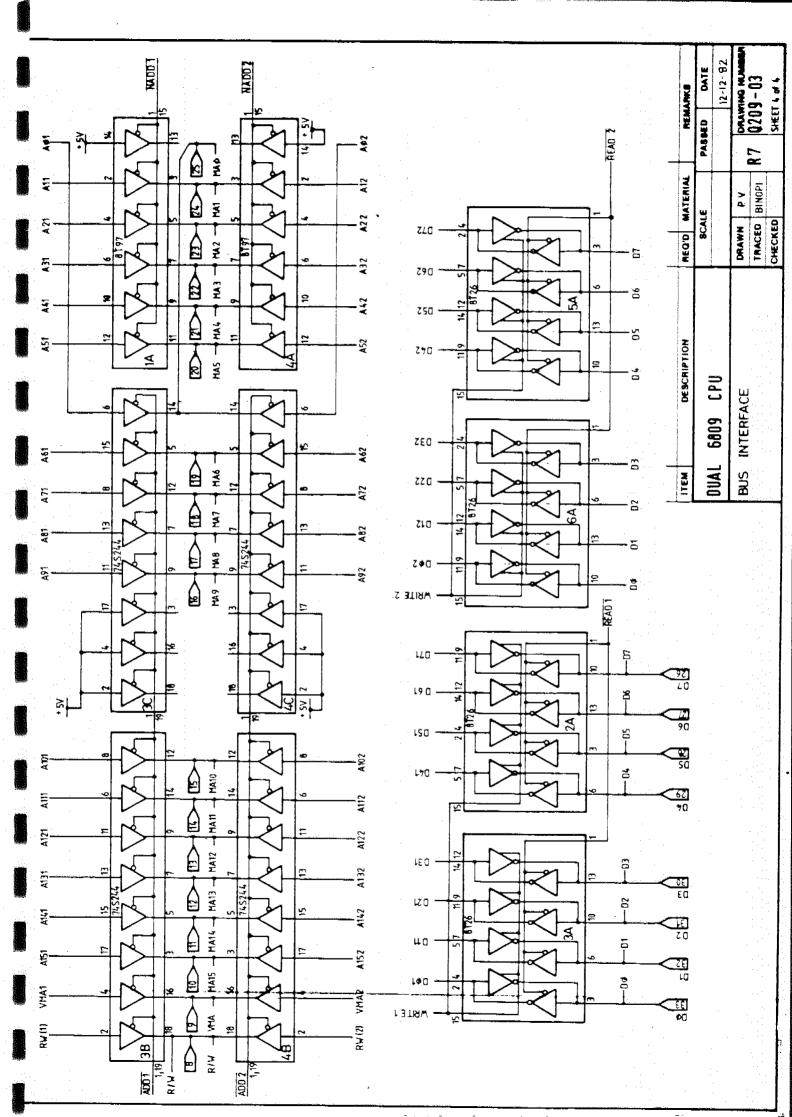

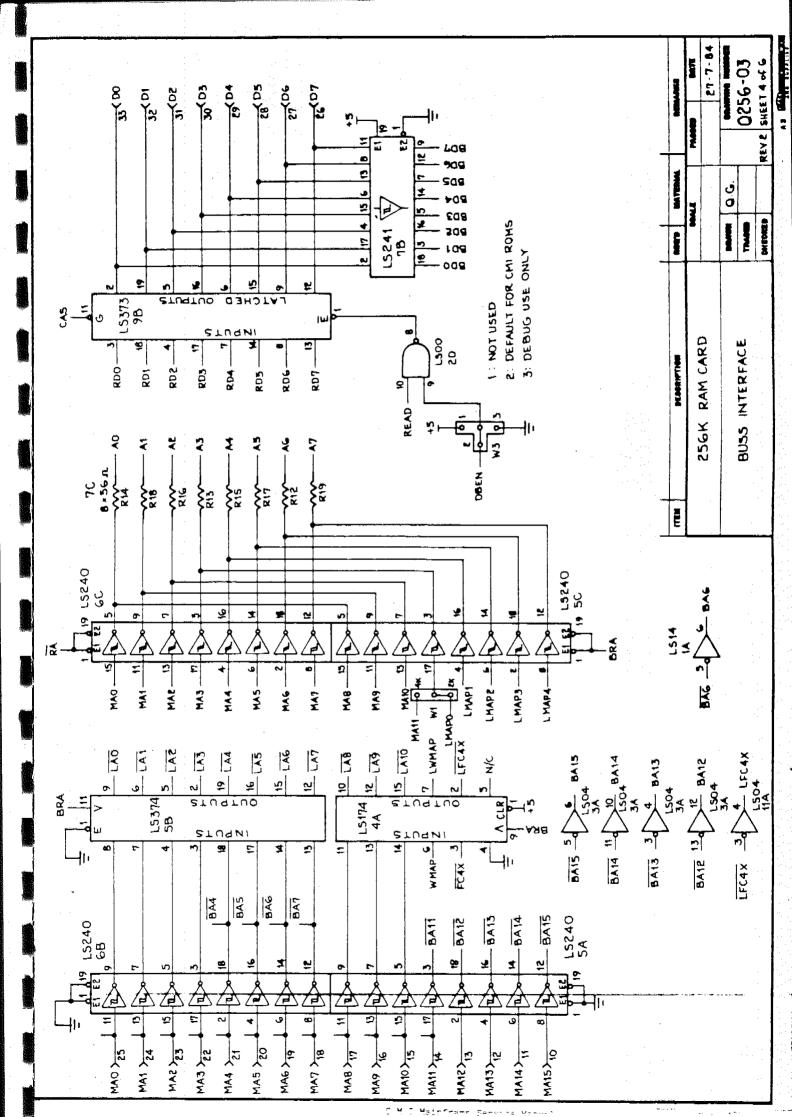

|     | 4.3.3 BUSS INTERFACE                            | 29   |

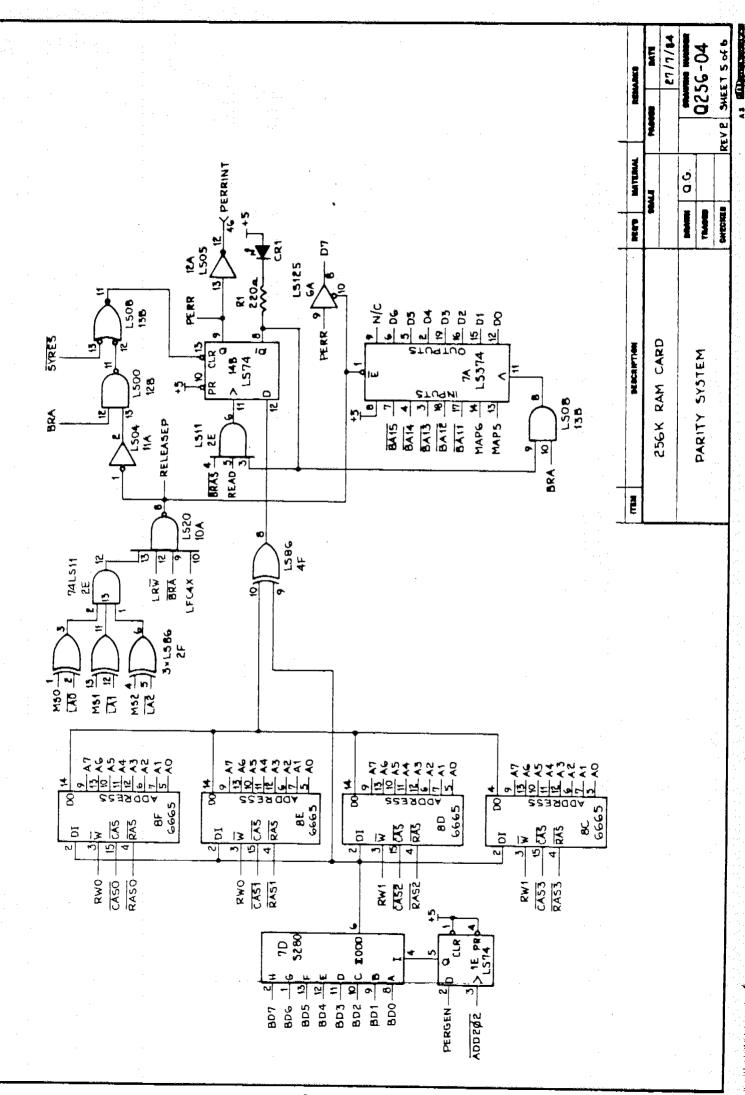

|     | 4.3.4 PARITY SYSTEM                             | 29   |

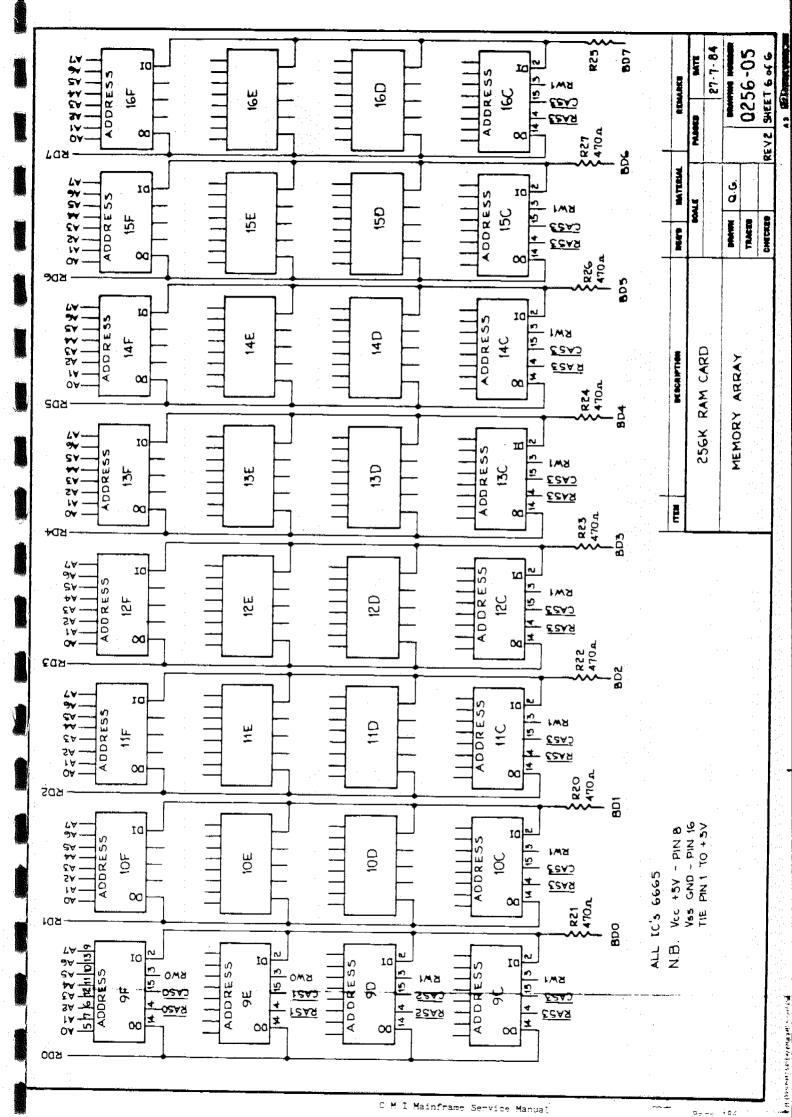

|     | 4.3.5 MEMORY ARRAY                              | 30   |

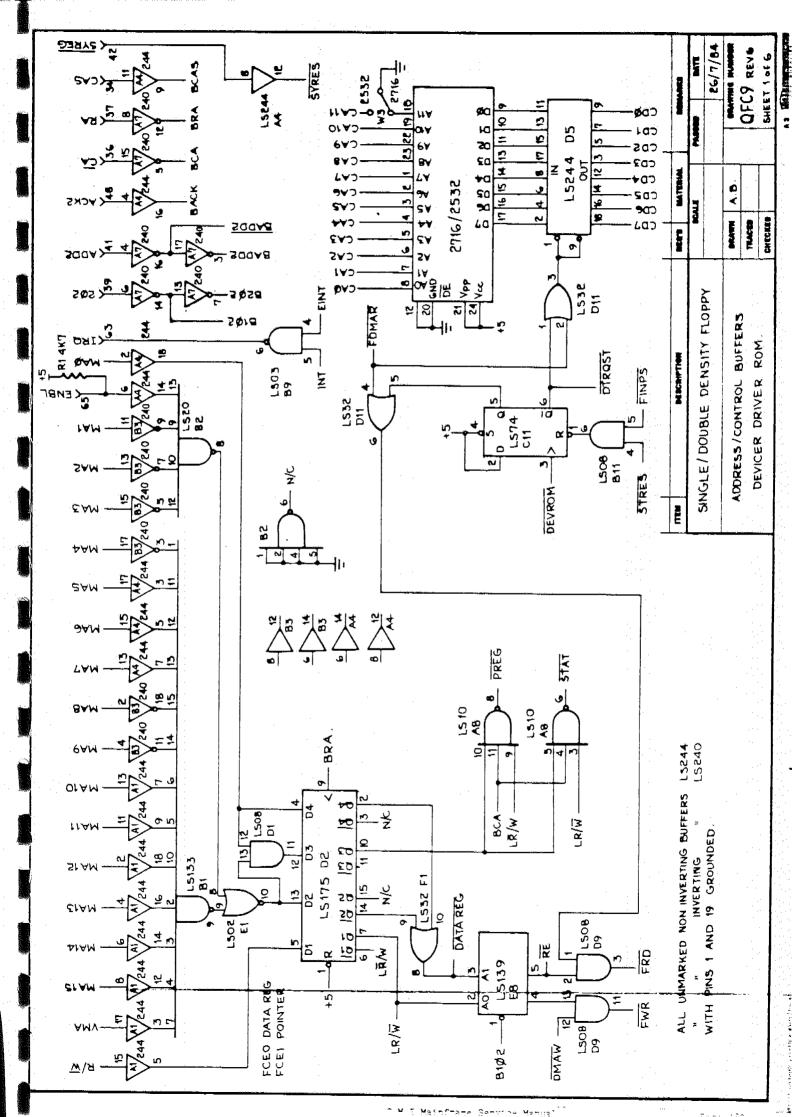

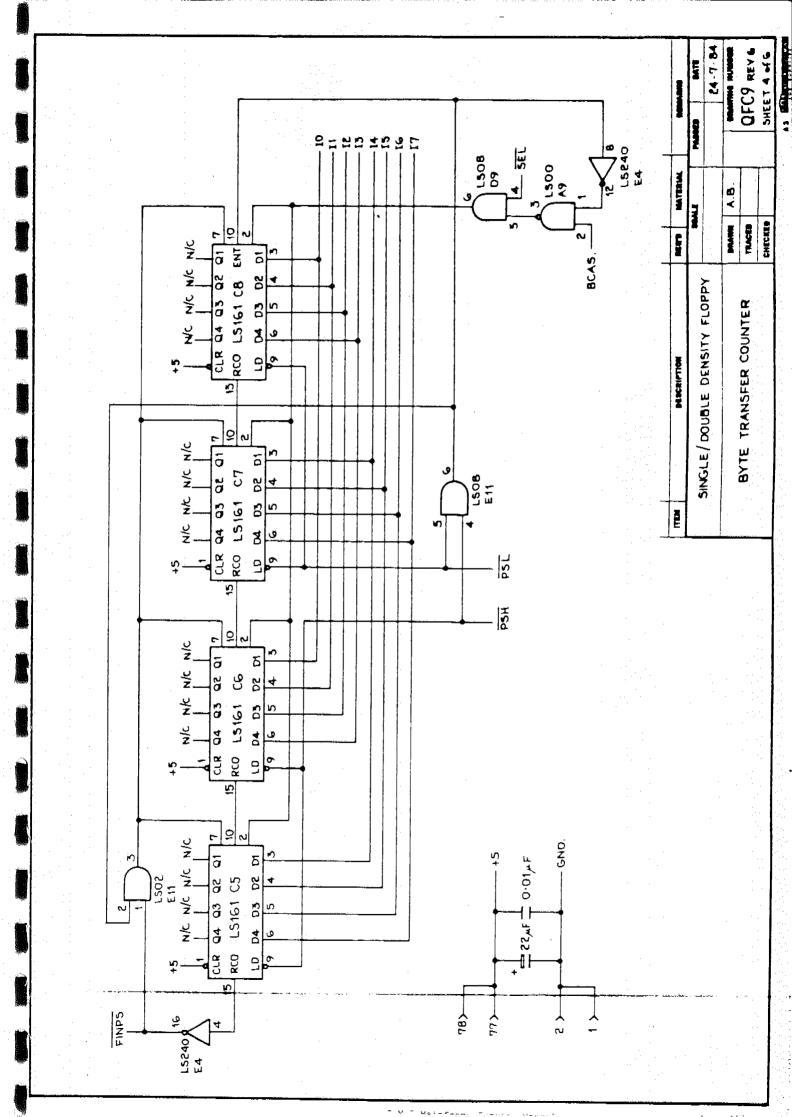

| 4.4 | QFC9 FLOPPY DISK CONTROL FUNCTIONAL DESCRIPTION | 31   |

|     | 4.4.1 INTRODUCTION                              | 31   |

|     | 4.4.1.1 Address Map                             | 32   |

|     | 4.4.1.2 Commands                                | 33   |

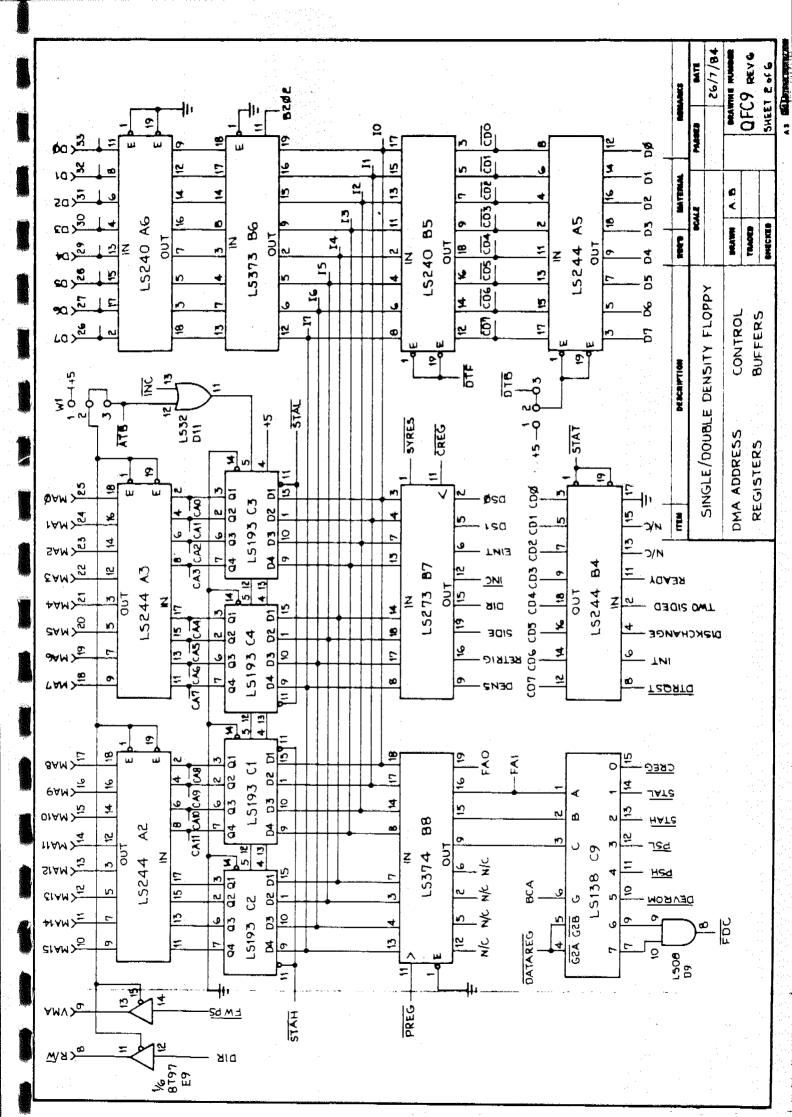

|     | 4.4.2 DATA BUFFERS, DMA ADDRESS COUNTER         | 33   |

|     | 4.4.2.1 DMA Address Counters                    | 33   |

|     | 4.4.2.2 DMA Byte transfer counters              | 33   |

|     | 4.4.2.3 Data Buffers                            | 34   |

|     | 4.4.3 ADDRESS DECODING, CONTROLLER L.S.I        | 34   |

|     | 4.4.3.1 Address Decoding                        | 34   |

|     | 4.4.3.2 Controller L.S.I.                       | 34   |

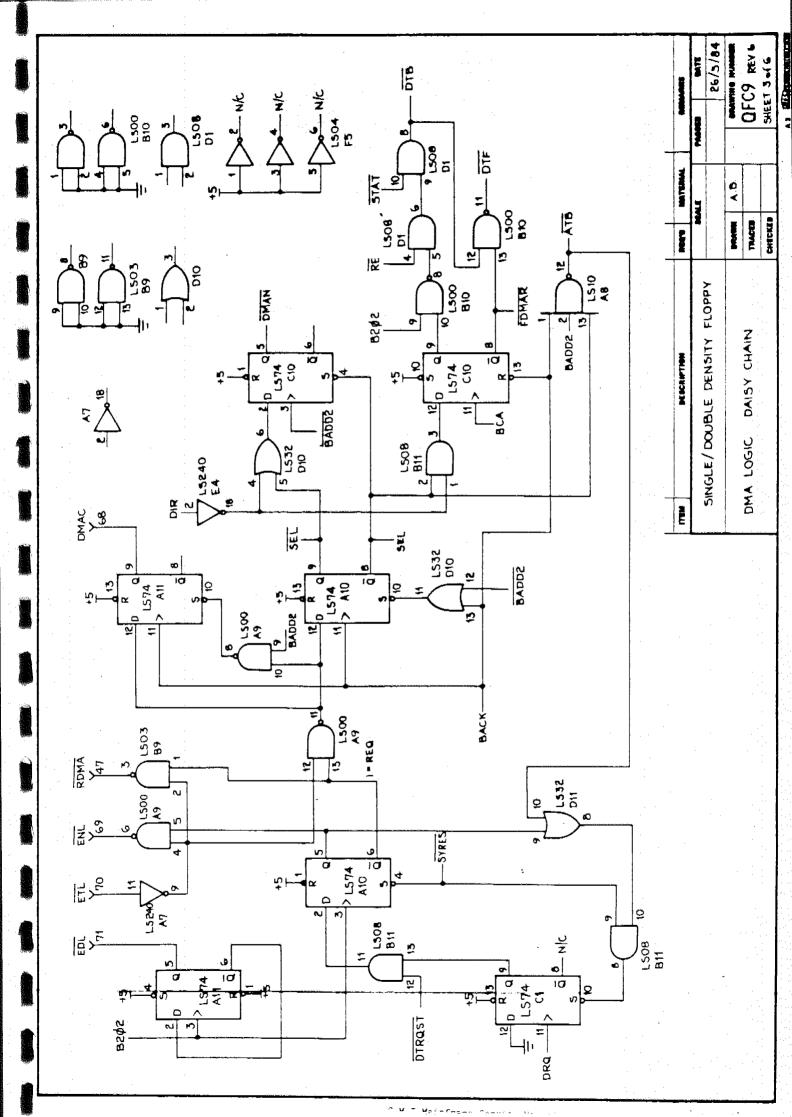

|     | 4.4.4 DMA LOGIC                                 | 34   |

|     | 4.4.5 CONTROL REGISTER                          | 35   |

|     | 4.4.6 MASTER OSCILLATOR                         | 35   |

|     | 4.4.7 WRITE PRECOMPENSATION                     | 35   |

|     | 4.4.8 DATA SEPARATOR                            | 36   |

|     | 4.4.9 DEVICE DRIVER ROM                         | 36   |

|     |        | Pag                                               | 56 |

|-----|--------|---------------------------------------------------|----|

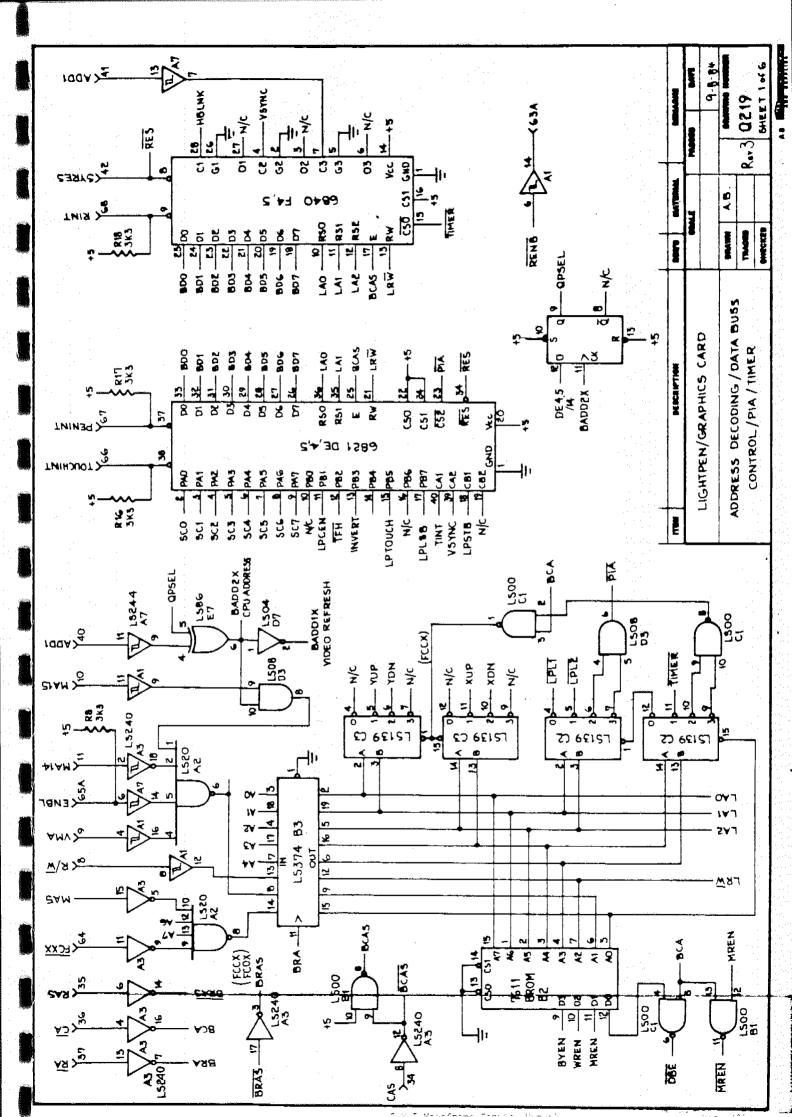

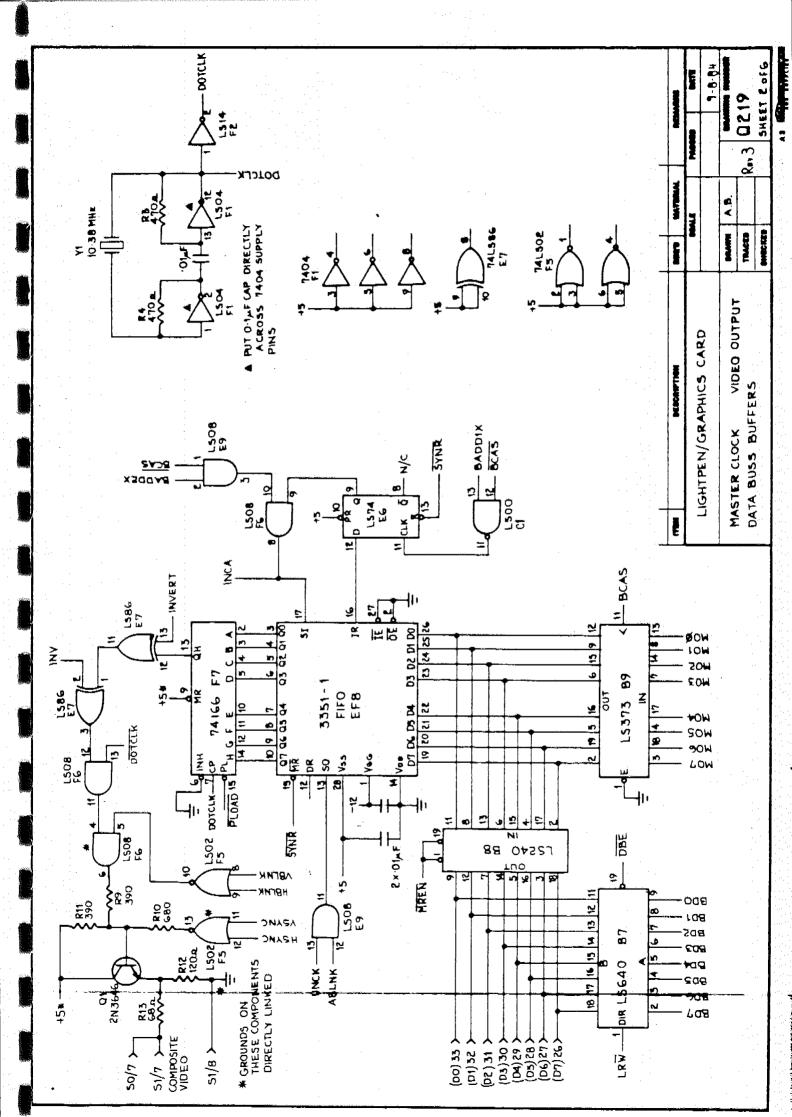

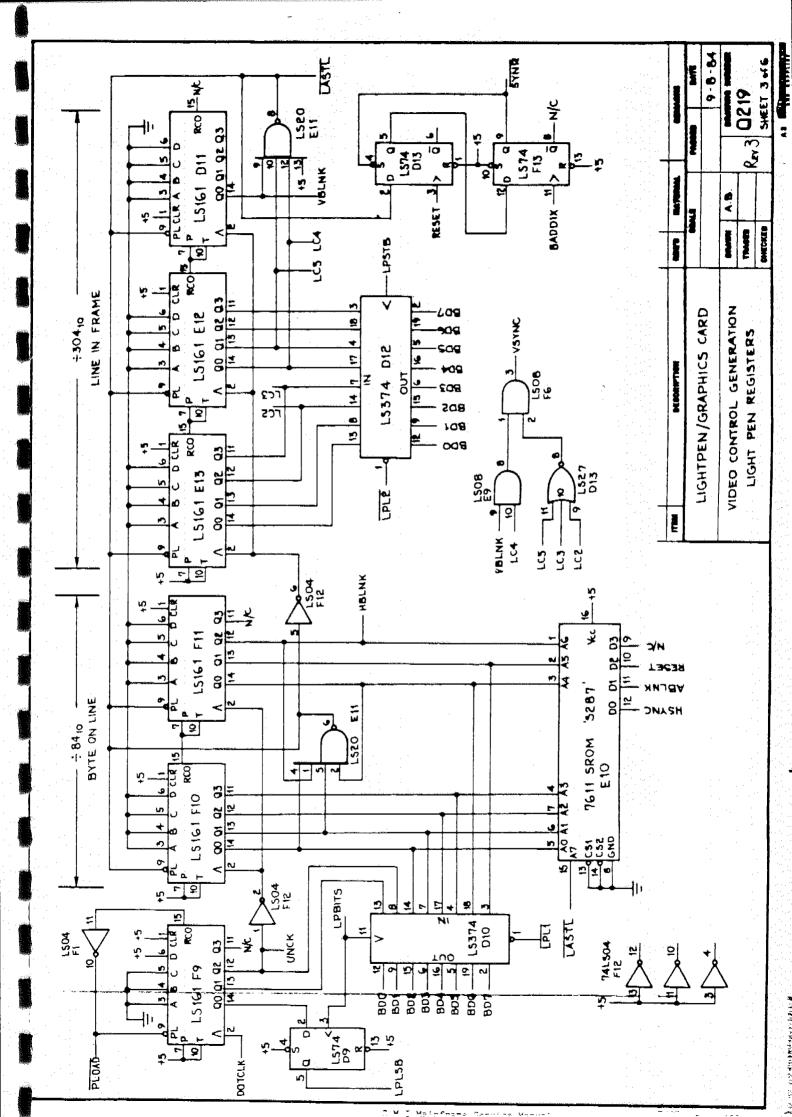

| 4.5 | Q219 I | IGHTPEN/GRAPHICS SYSTEM FUNCTIONAL DESCRIPTION 37 |    |

|     | 4.5.1  | INTRODUCTION 37                                   | ,  |

|     | 4.5.2  | VIDEO TIMING LOGIC 38                             | 3  |

|     |        | 4.5.2.1 Dot Clock Generation                      | 3  |

|     |        | 4.5.2.2 Video FIFO and Shift Register 38          | 3  |

|     |        | 4.5.2.3 Video Output                              | )  |

|     | 4.5.3  | SELECT LOGIC AND DATA CONTROL 39                  |    |

|     |        | 4.5.3.1 Address Decoding 39                       |    |

|     |        | 4.5.3.2 Data Buffers 40                           |    |

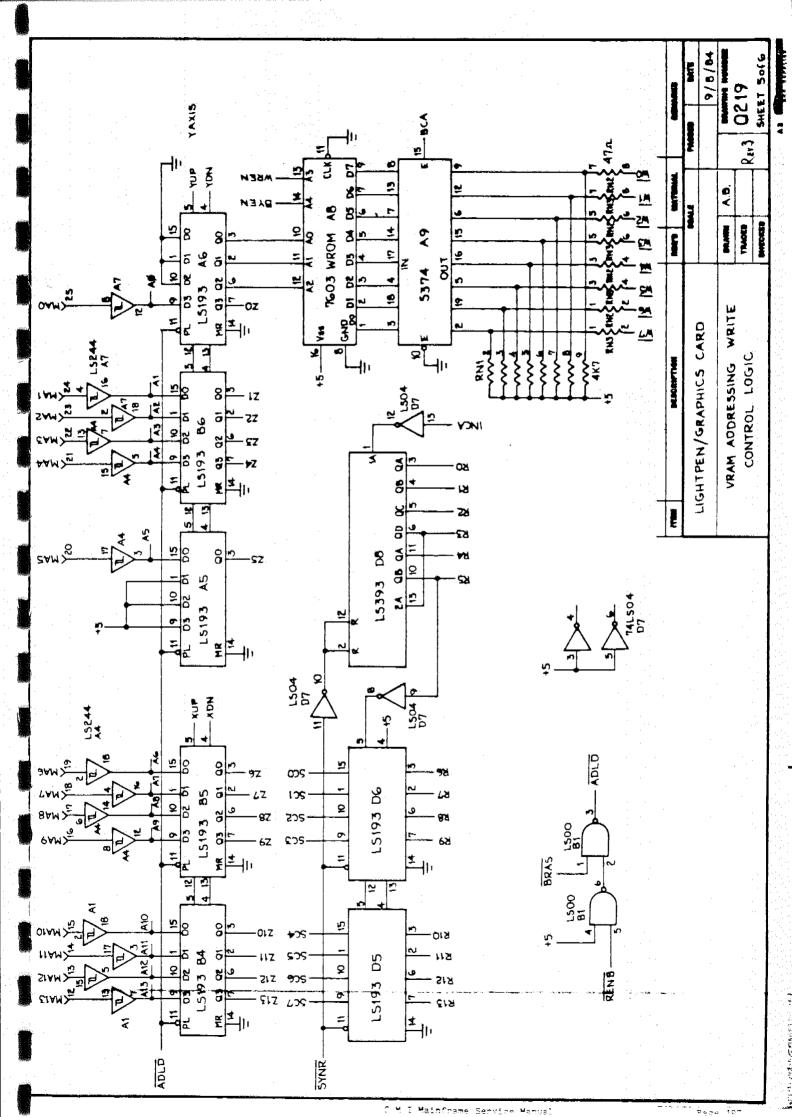

|     | 4.5.4  | VRAM ADDRESSING LOGIC 40                          |    |

|     | Harris | 4.5.4.1 Addressing Counters                       | )  |

|     |        | 4.5.4.2 Bit Selection                             |    |

|     |        | 4.5.4.3 Vertical Scrolling                        |    |

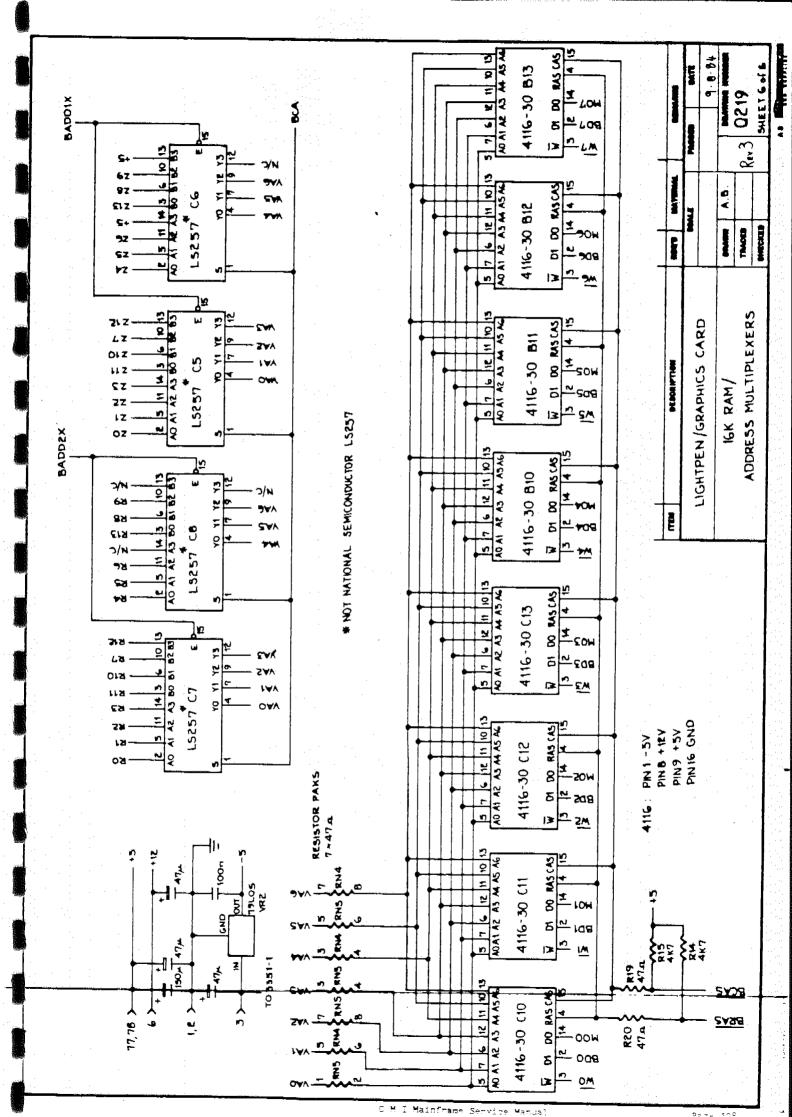

|     | 4.5.5  | VRAM Addressing Multiplexing41                    |    |

|     |        | LIGHT PEN 41                                      |    |

|     | 11.15  | 4.5.6.1 Introduction                              |    |

|     | 4.5.7  | CO-ORDINATE COUNTERS, DEGLITCHER, PIA, TIMER 42   |    |

|     |        | 4.5.7.1 Hit Deglitcher 42                         |    |

|     |        | 4.5.7.2 Hit and Touch Receivers 42                |    |

|     |        | 4.5.7.3 Co-ordinate Latches                       |    |

|     |        | 4.5.7.4 Control PIA                               |    |

|     |        | 4.5.7.5 Timer 43                                  |    |

|     | 4.5.8  | VIDEO MEMORY VRAM                                 |    |

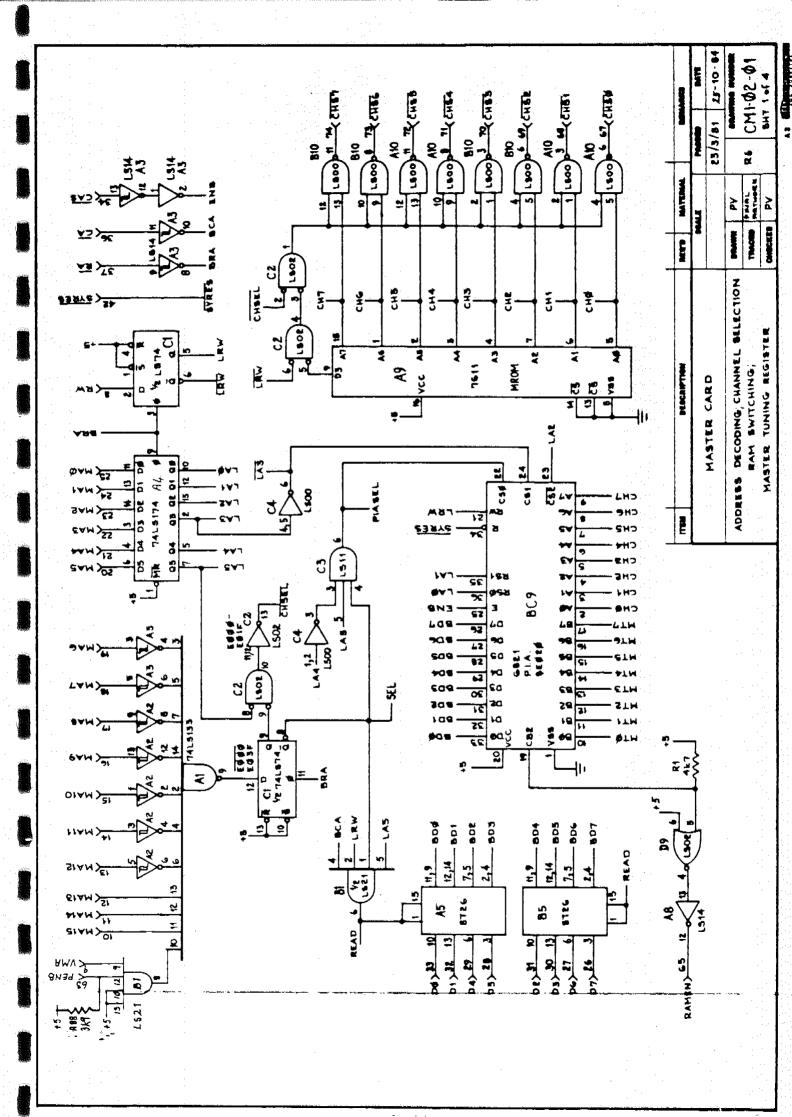

| 4.6 |        | MASTER CARD FUNCTIONAL DESCRIPTION 44             | ٠. |

| 3   |        | INTRODUCTION                                      | 1  |

|     |        | ADDRESS DECODING, CHANNEL SELECTION,              |    |

|     |        | MASTER TUNING REGISTER                            | 1  |

|     |        | 4.6.1.1 Address Decoding                          | ļ  |

|     |        | 4.6.1.2 Channel Selection 44                      | ı  |

|     |        | 4.6.1.3 Master Tuning Register                    | ;  |

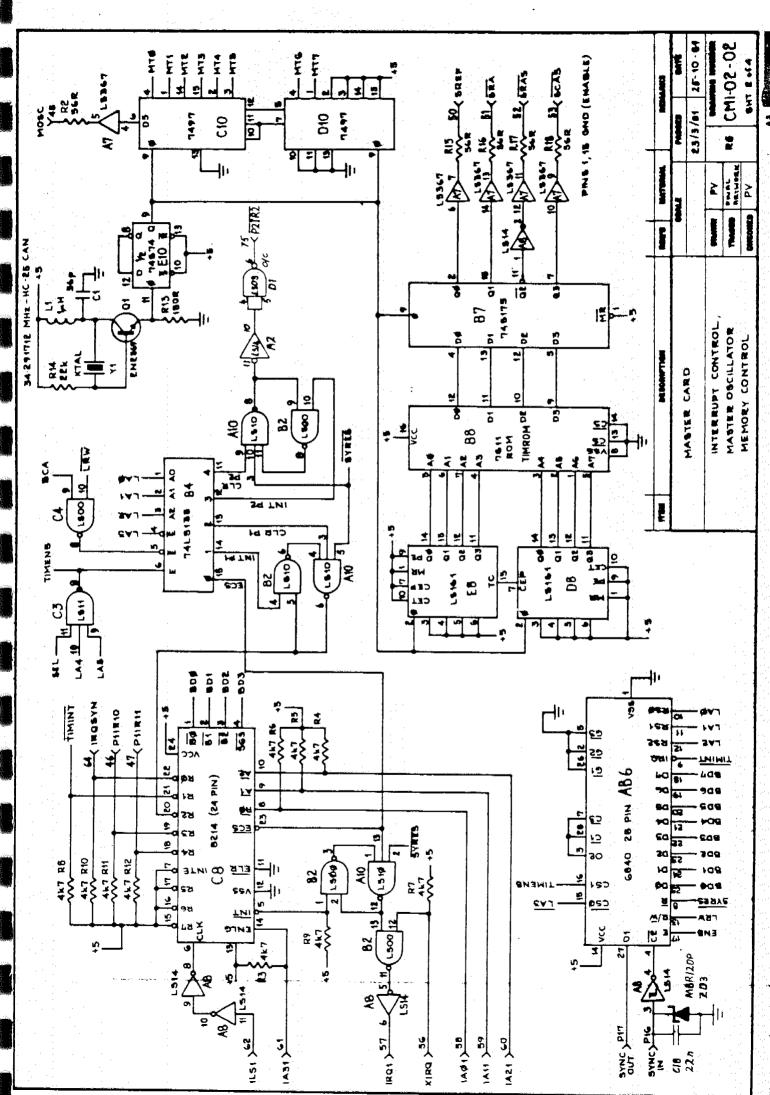

|     | 4.6.2  | INTERRUPT CONTROL, MASTER OSCILLATOR,             |    |

|     |        | MEMORY CONTROL 45                                 | i  |

|     |        | 4.6.2.1 Interrupt Control                         |    |

|     |        | 4.6.2.2 Master Oscillator 45                      |    |

|     |        | 4.6.2.3 Memory Control                            |    |

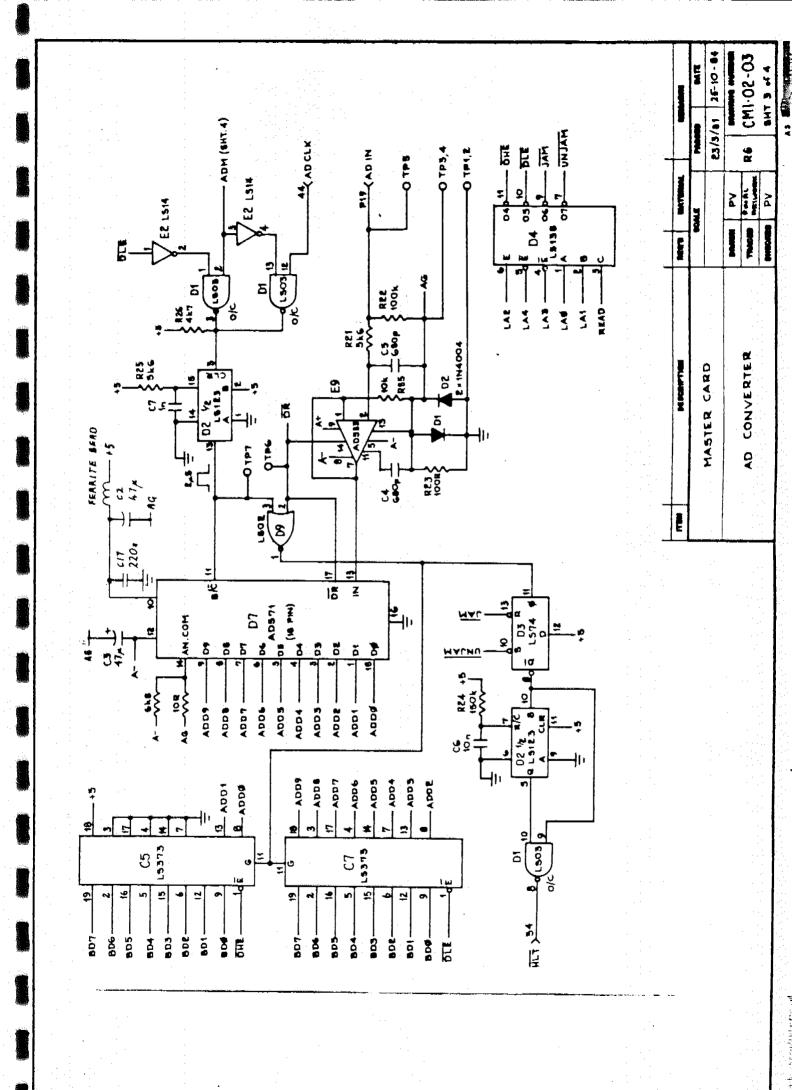

|     | 4.6.3  | ANALOG TO DIGITAL CONVERTER 46                    |    |

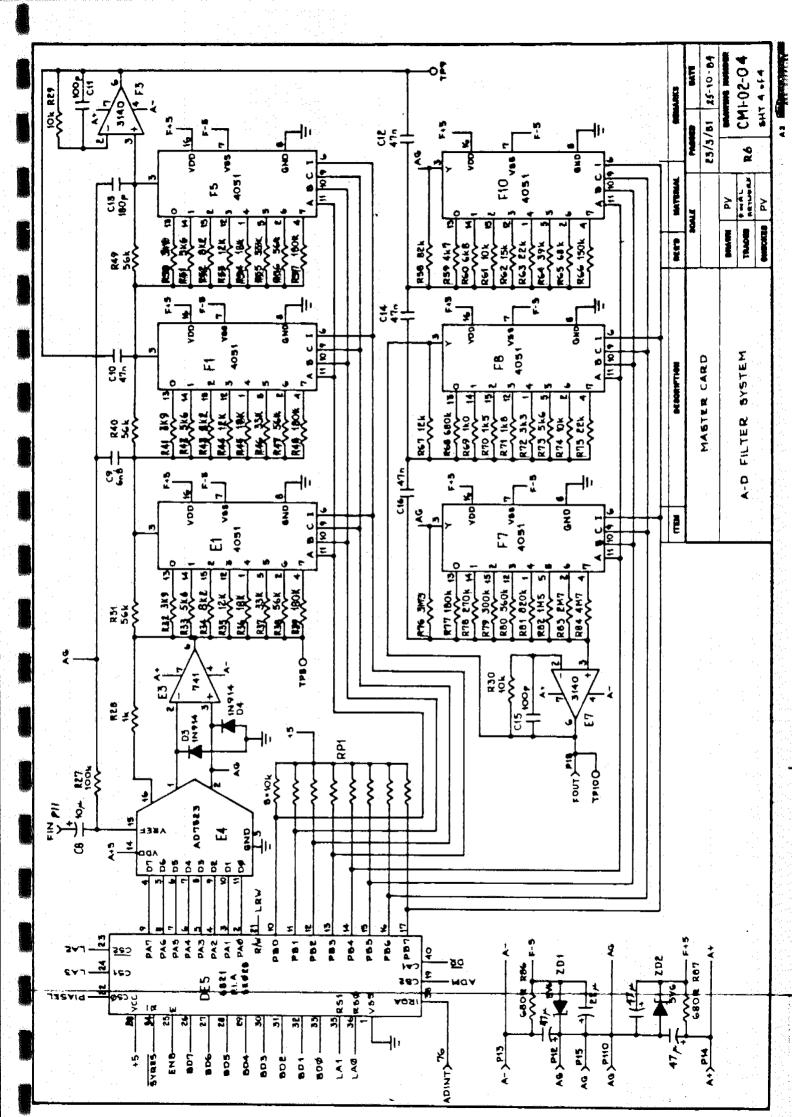

|     |        | A-D FILTER SYSTEM 46                              | )  |

| 4.7 |        | -A CHANNEL CARD FUNCTIONAL DESCRIPTION 47         | ,  |

|     |        | INTRODUCTION 47                                   |    |

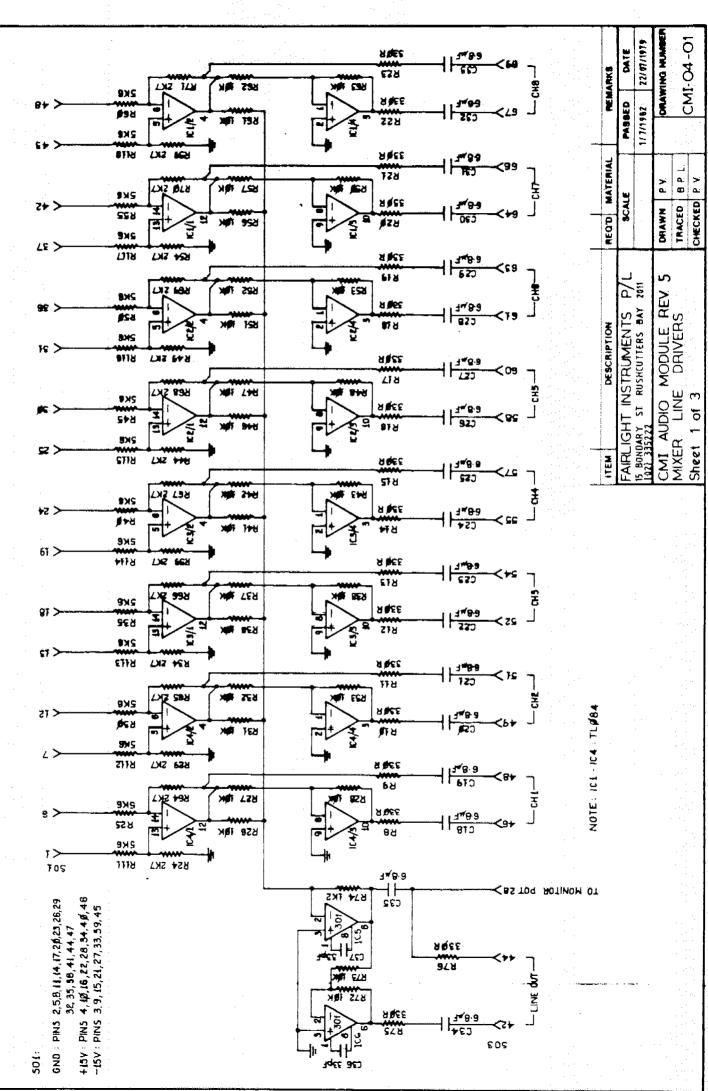

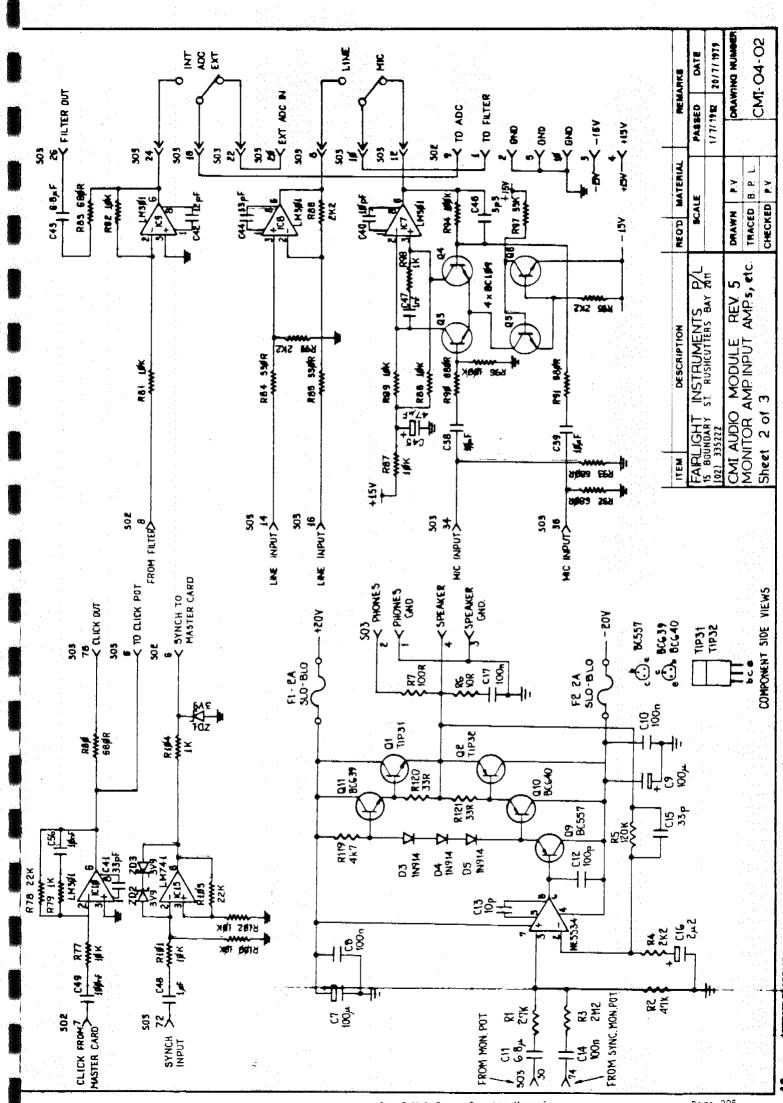

| 4.8 |        | AUDIO MODULE FUNCTIONAL DESCRIPTION 48            |    |

|     |        | INTRODUCTION 48                                   |    |

|     |        | MIXER, LINE DRIVERS 48                            |    |

|     | 2      | 4.8.2.1 Mixer                                     |    |

|     |        | 4.8.2.2 Line Drivers                              |    |

|     | 4.8.3  | MONITOR AMP, INPUT AMPS, SYNC IN/OUT 48           |    |

|     |        | 4.8.3.1 Monitor Amplifier                         |    |

|     |        | 4.8.3.2 Input Amplifiers                          |    |

|     |        | 4.8.3.3 Sync In/Out                               |    |

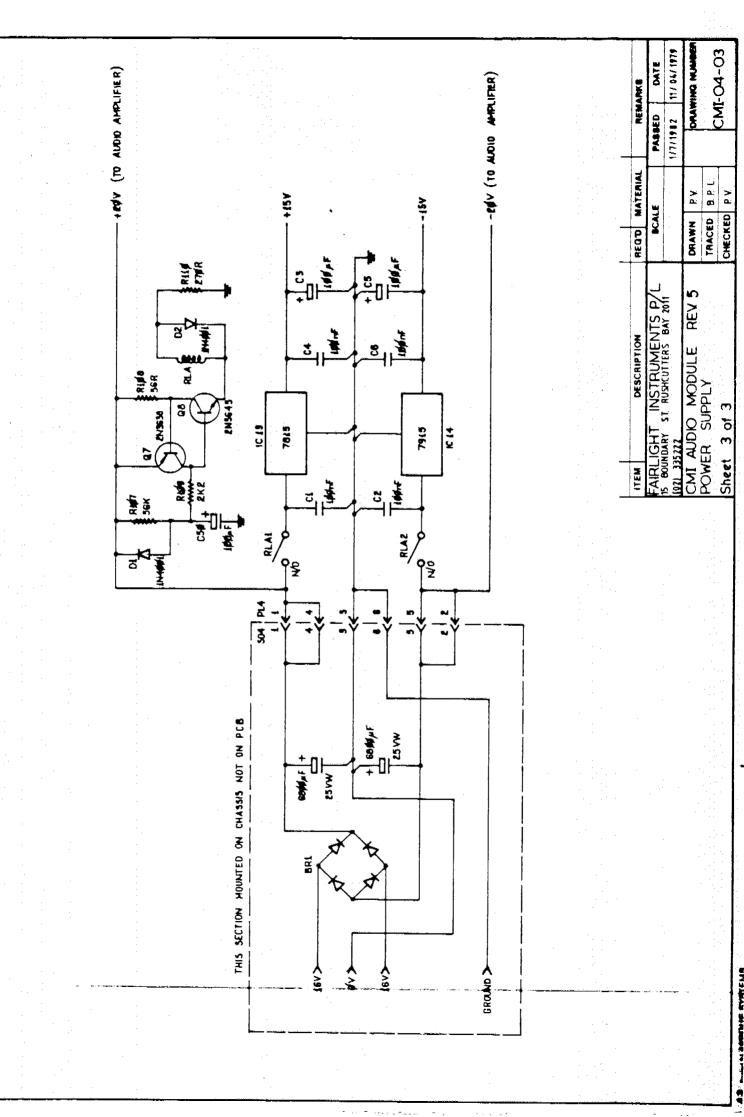

|     | 4.8.4  | POWER SUPPLY 49                                   |    |

|     |        |                                                   |    |

|    | I C ODG A TANKER OF THE CONTROL OF T | Pag      |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

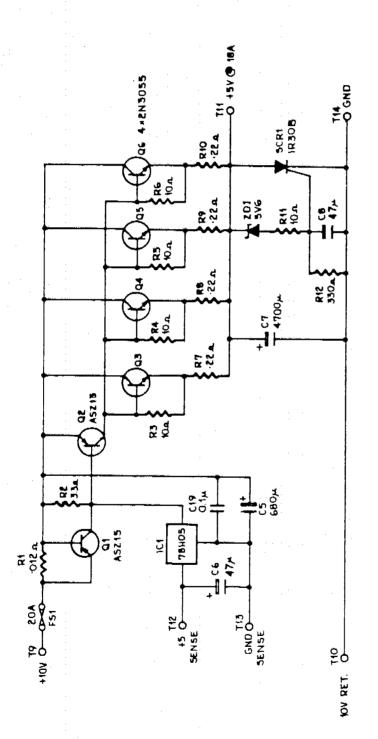

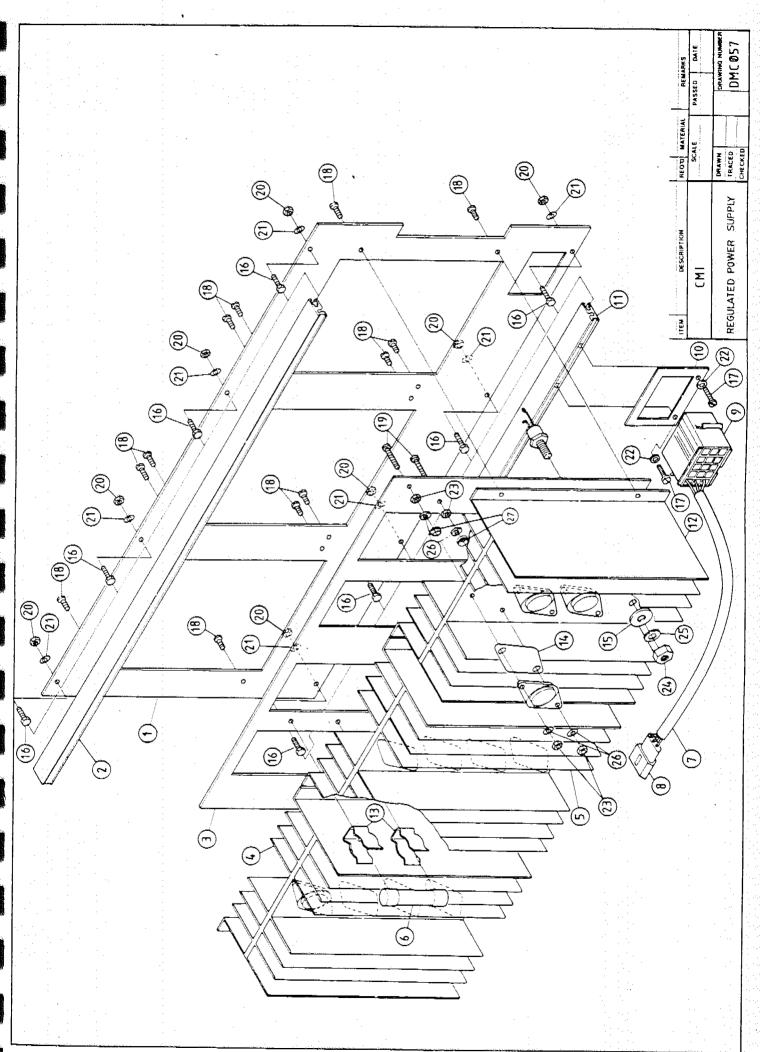

|    | 4.9 QPSA POWER SUPPLY FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 50     |

|    | 4.9.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50       |

|    | 4.9.2 UNREGULATED SUPPLIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50       |

|    | 4.9.3 REGULATOR 5 VOLT 18 AMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50       |

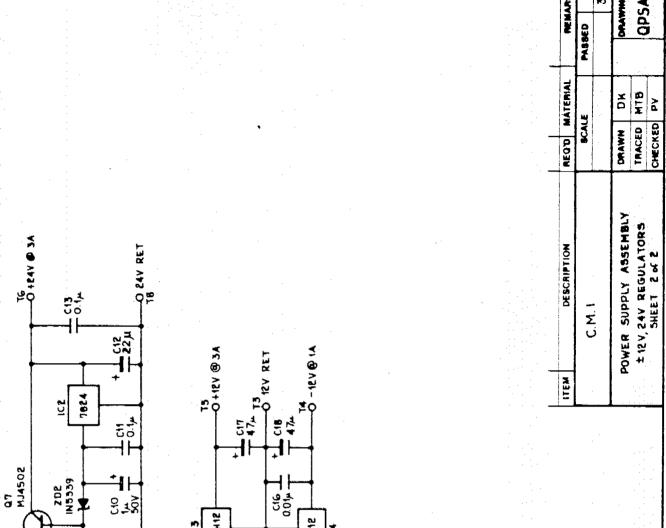

|    | 4.9.4 + 12 VOLT, 24 VOLT SUPPLIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51       |

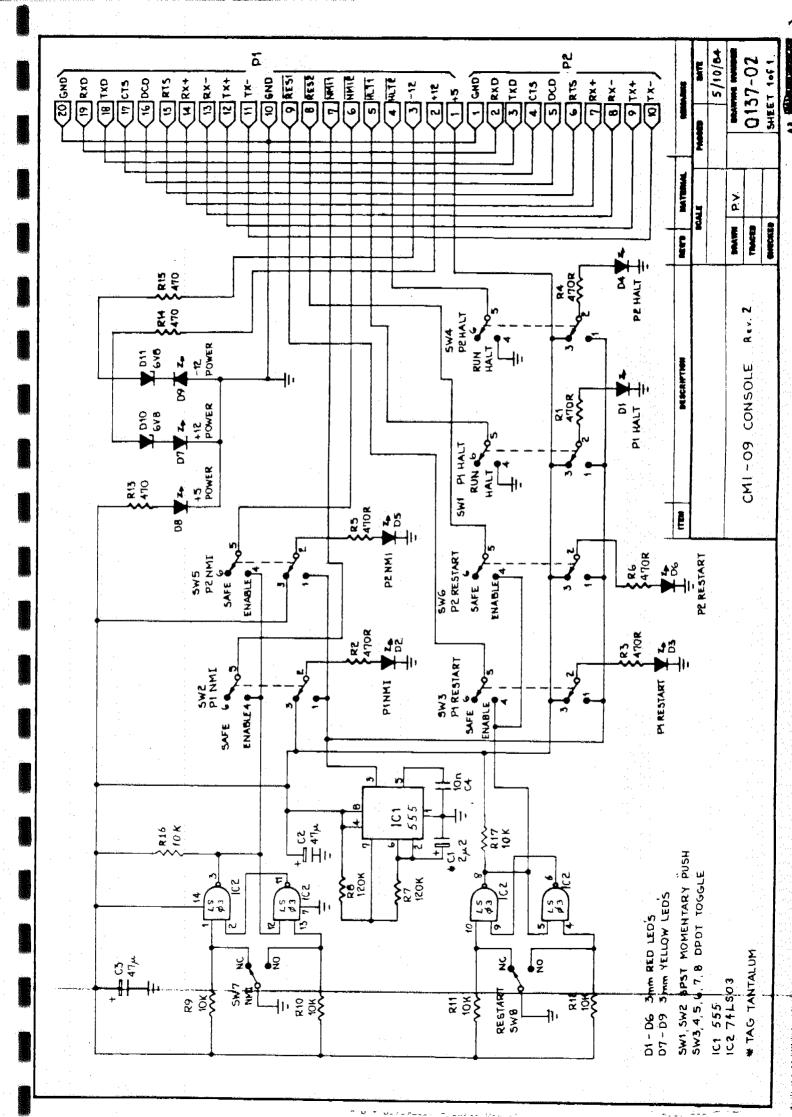

|    | 4.10 Q137 FRONT PANEL FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52       |

|    | 4.10.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | - 52     |

|    | 4.10.1.1 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52       |

|    | 4.10.2 COMMUNICATIONS PORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52       |

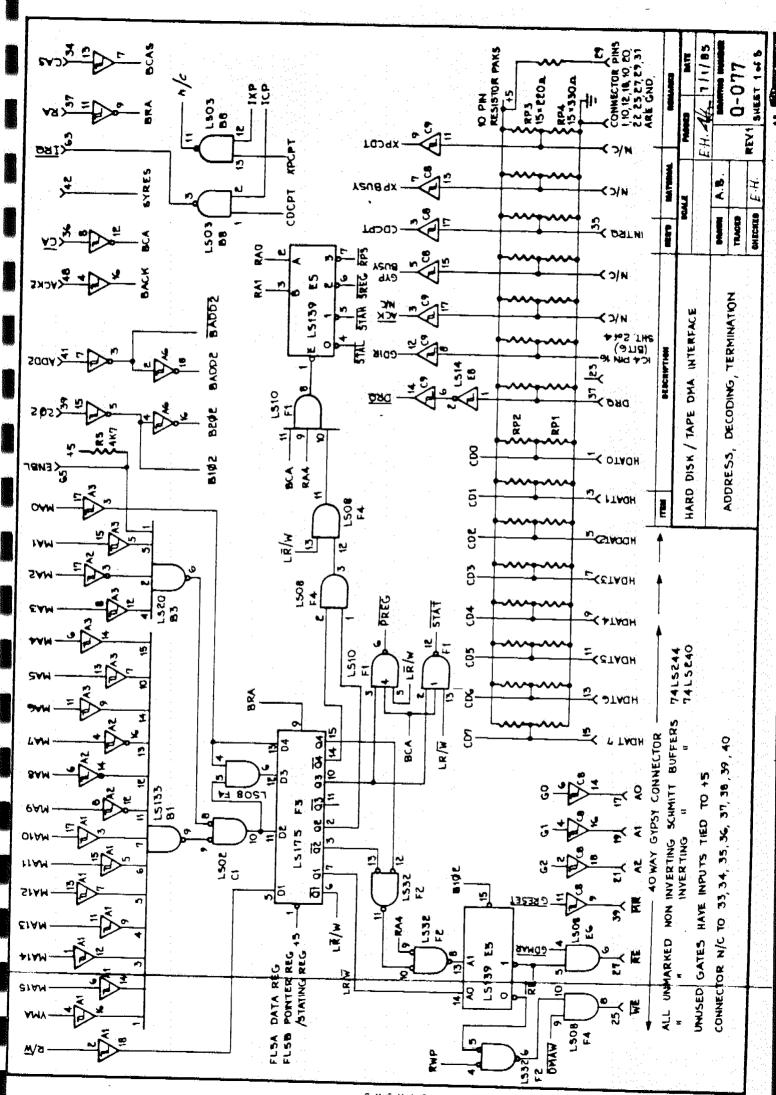

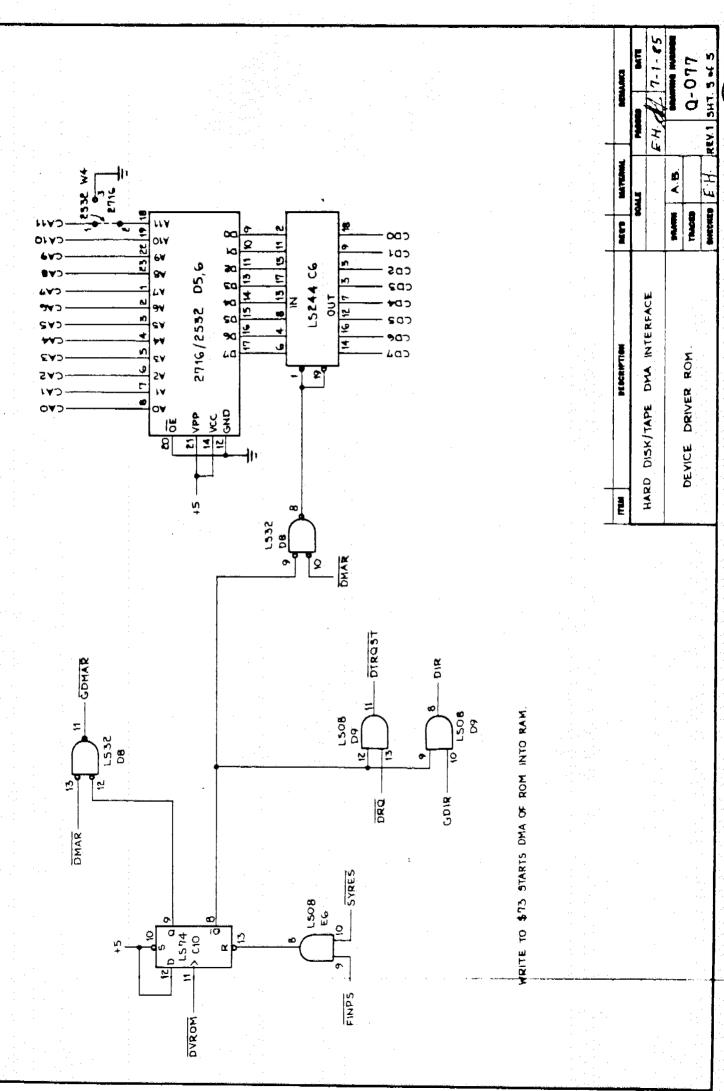

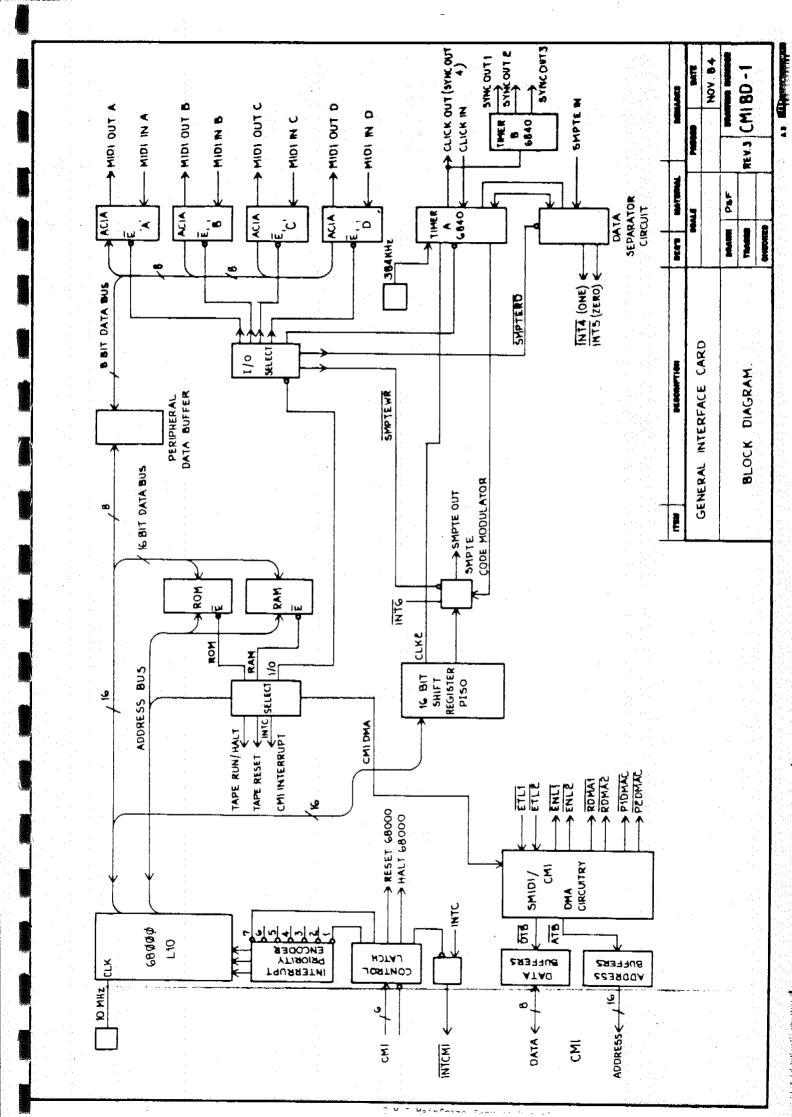

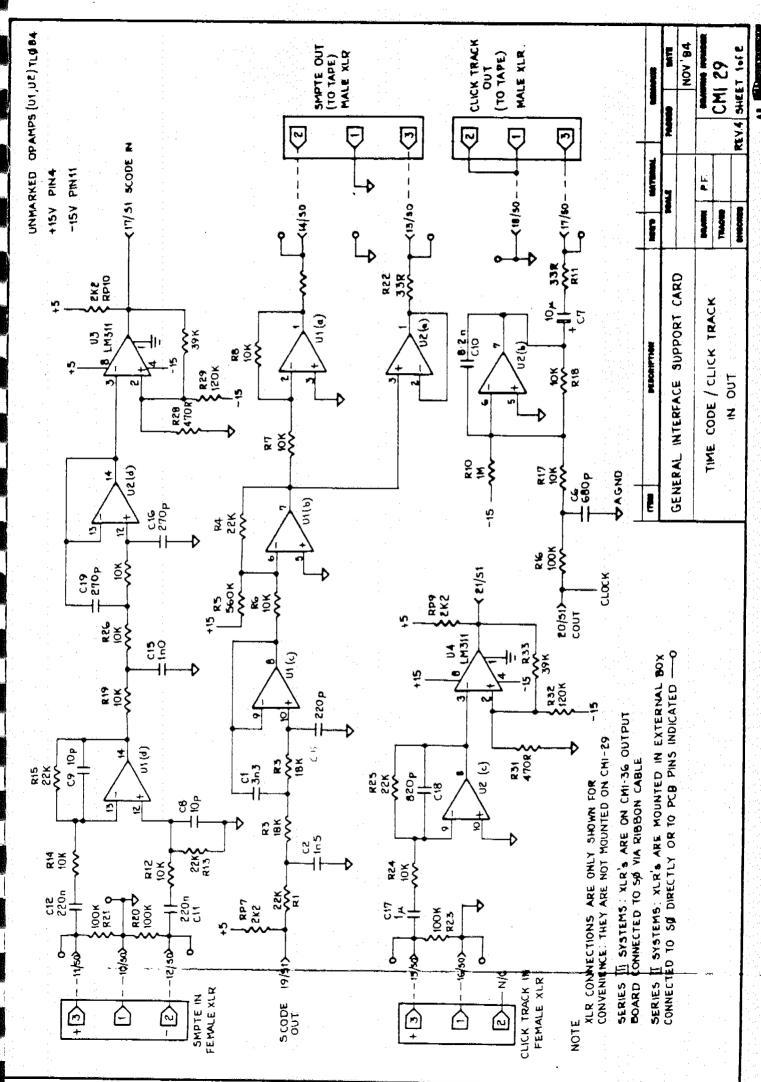

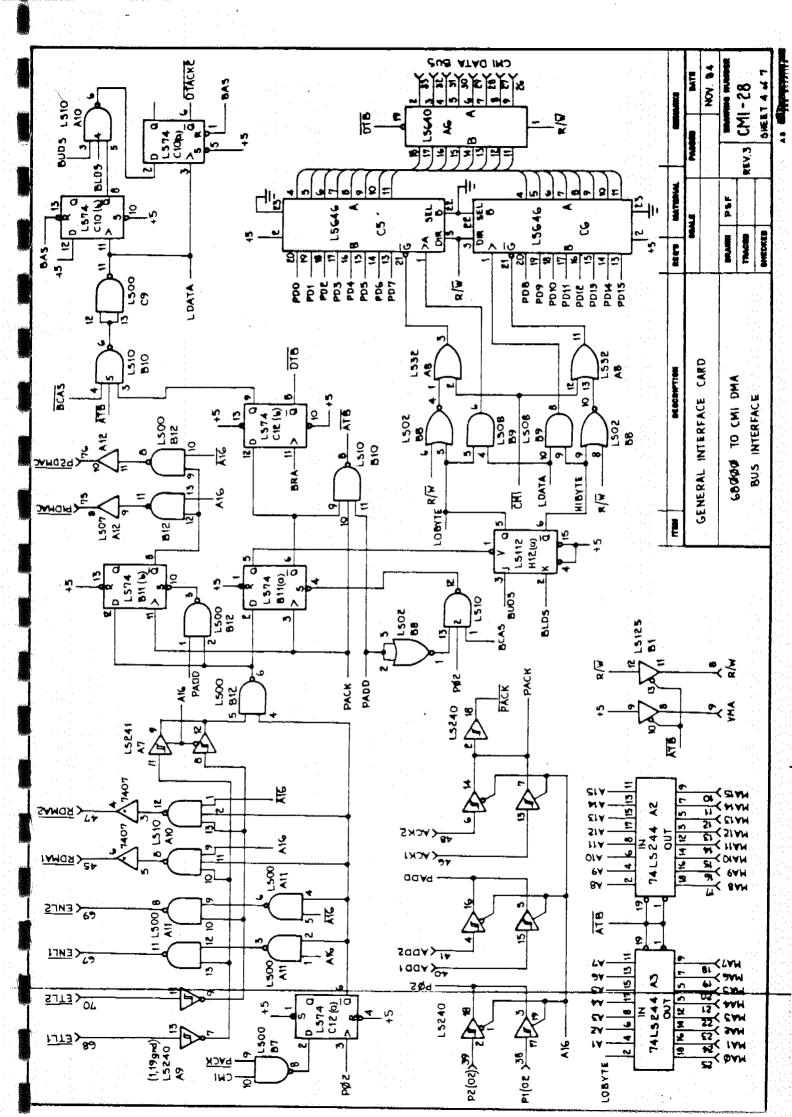

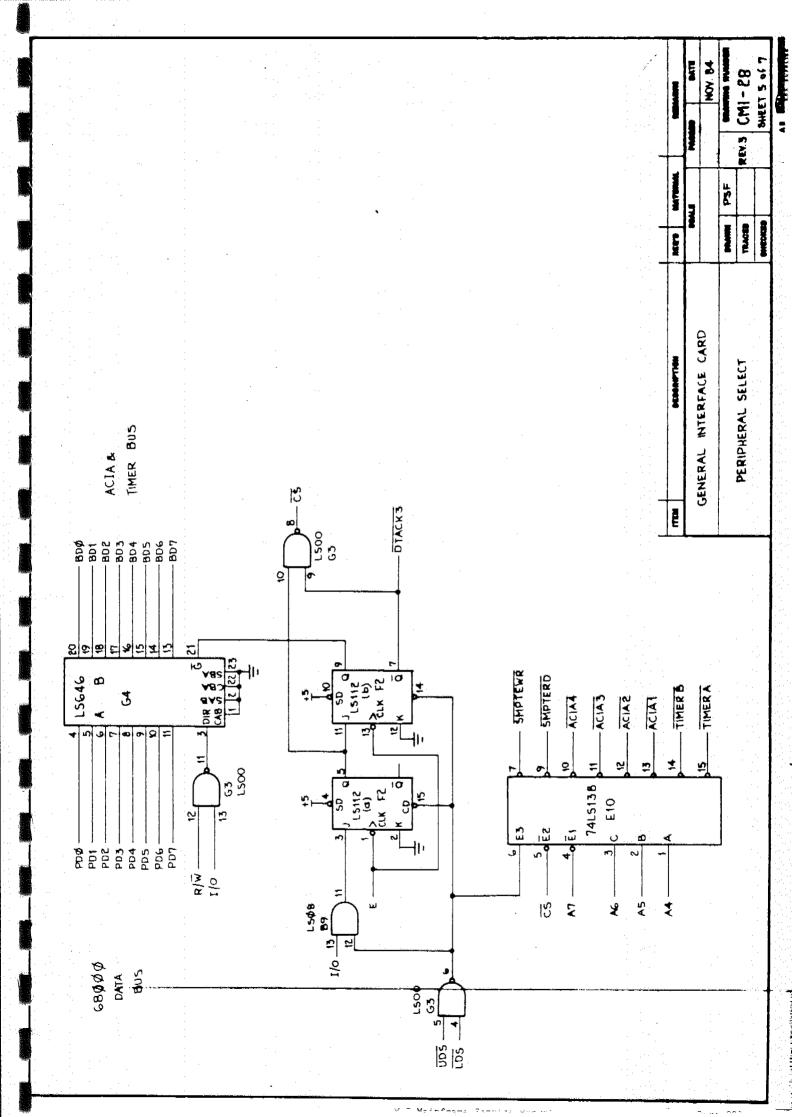

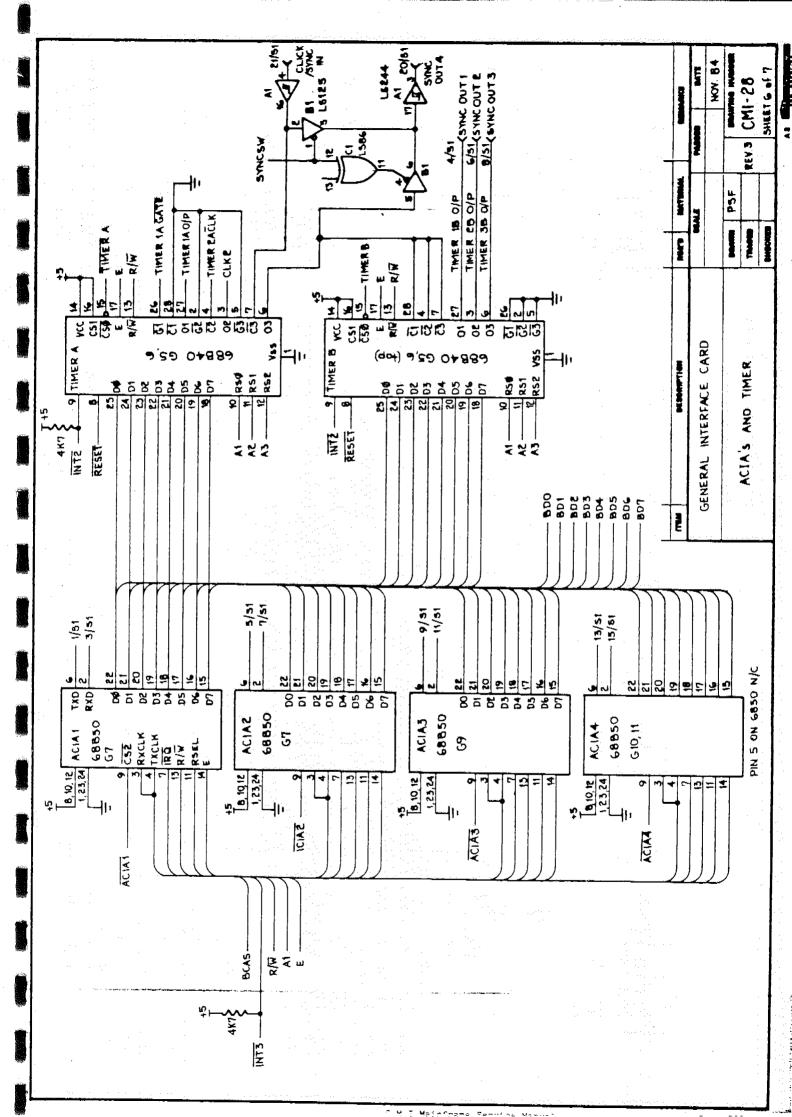

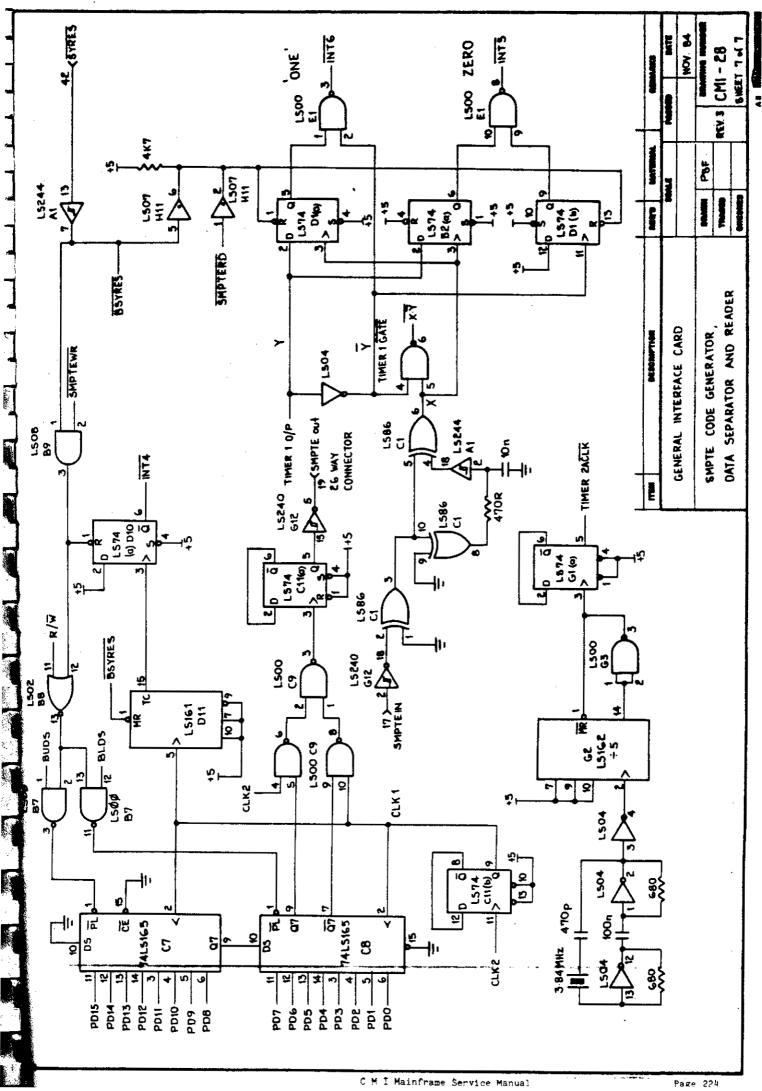

|    | 4.11 Q077 HARD DISK CONTROLLER DMA INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|    | FUNCTIONAL DESCRIPTIONAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53       |

|    | 4.11.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 53       |

|    | 4.11.2 ADDRESS MAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53       |

|    | 4.11.3 COMMANDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 54     |

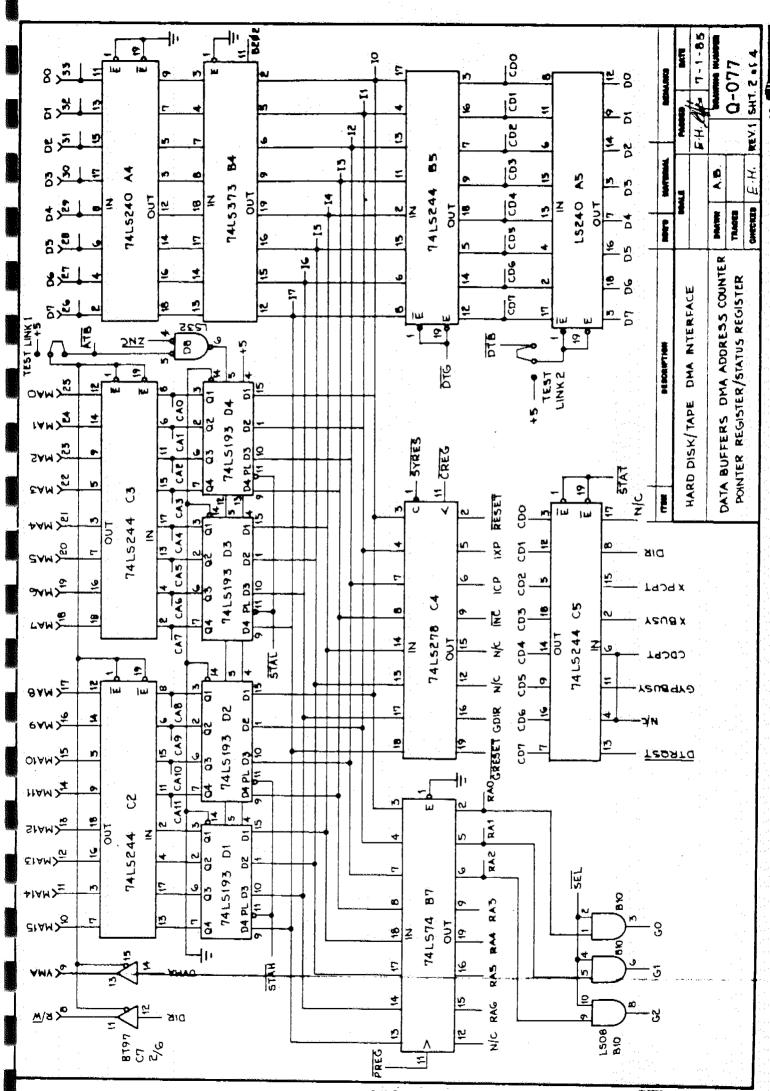

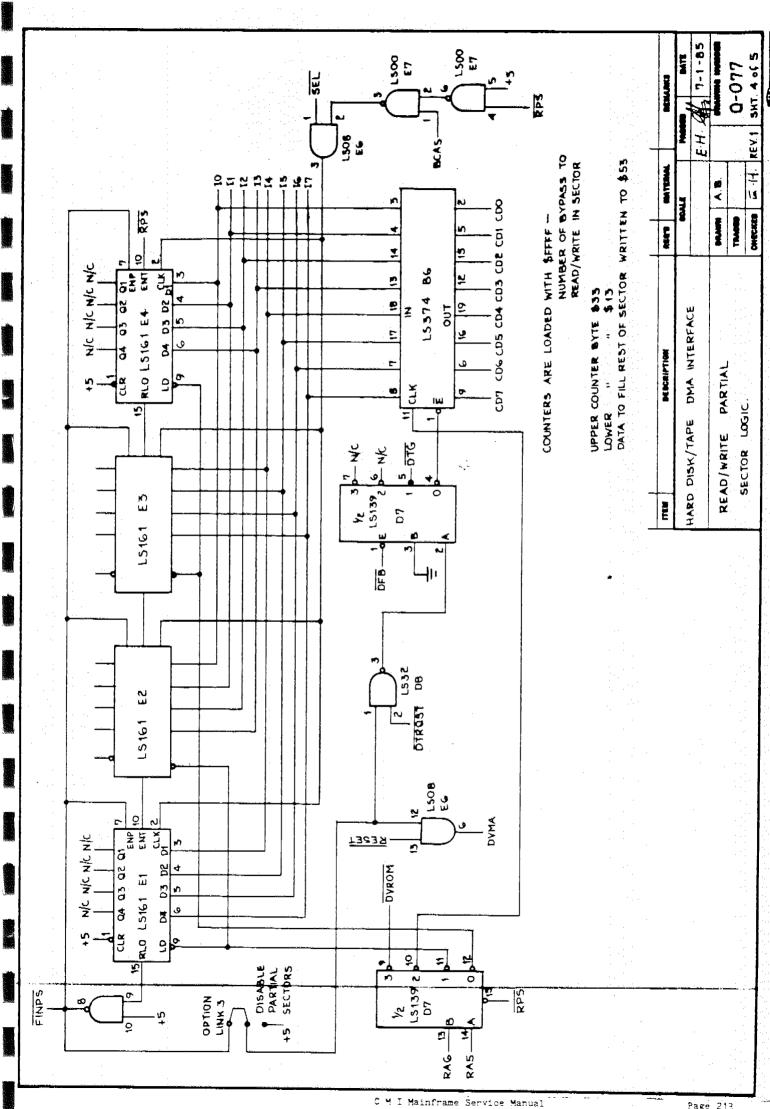

|    | 4.11.4 DMA ADDRESS COUNTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54       |

|    | 4.11.5 DMA BYTE TRANSFER COUNTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74<br>55 |

|    | 4.11.6 DATA BUFFERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55       |

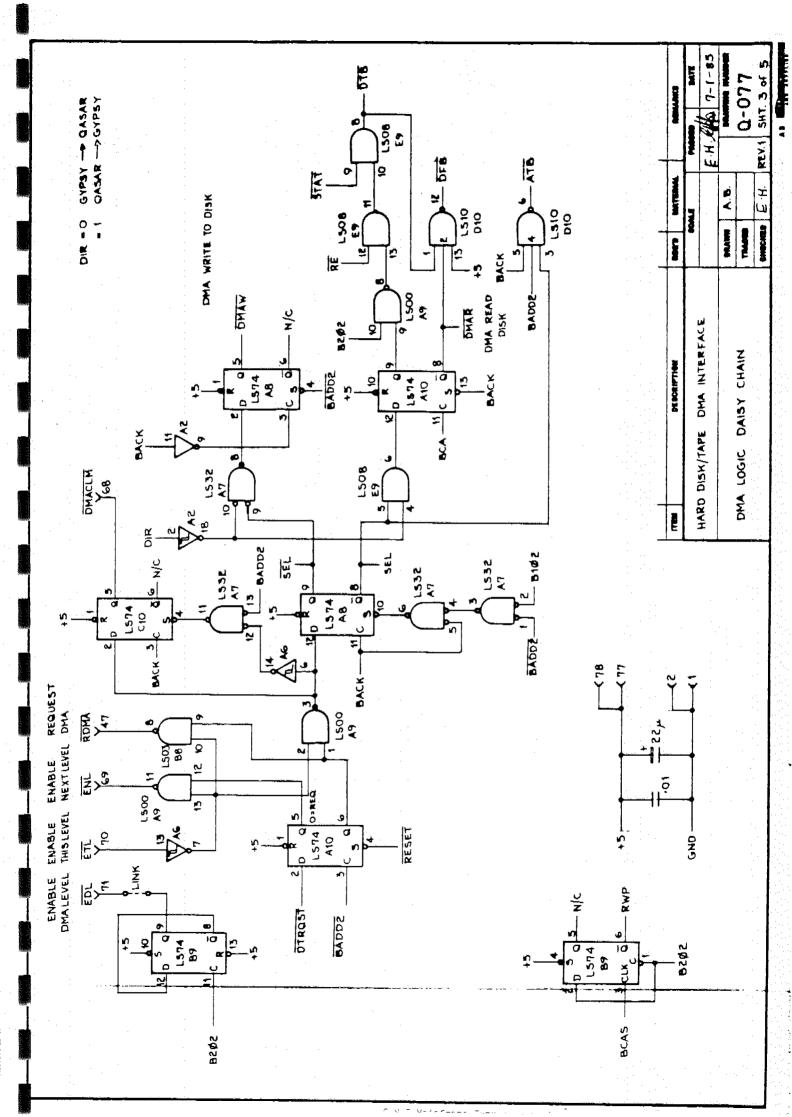

|    | 4.11.8 DMA LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 55       |